Learn why this is the correct answer

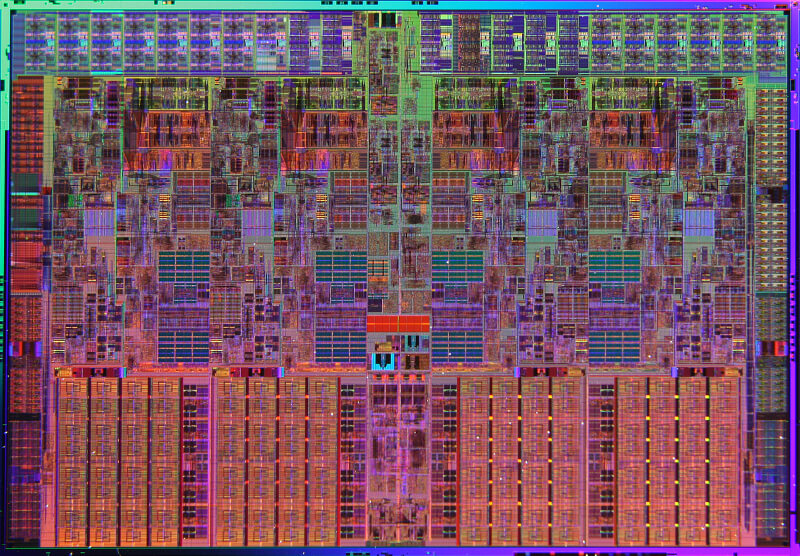

Although many microprocessors such as IBM's POWER5 and AMD's Athlon 64 already had built-in memory controllers, Intel first made the move in 2008 with its Nehalem architecture, which shipped with an integrated memory controller that supported three memory channels of DDR3 SDRAM.

Prior to Nehalem's arrival, a 333MHz FSB limited high-end Core 2 processors to a peak memory bandwidth of 10.6GB/s while DDR2-1066 memory running in dual-channel topped out at 17GB/s. In stark contrast, when we reviewed the first Nehalem parts, their integrated controller offered a peak bandwidth of 25.5GB/s to 31GBs with DDR3-1066 or DDR3-1333 RAM.

Along with other architectural improvements and the resurrection of HyperThreading, Nehalem made for an exciting follow-up to Intel's 'Core' series parts.