Something to look forward to: Last year, AMD released the Ryzen 7 5800X3D, featuring new "3D V-Cache" technology. The chiplet cache design allowed AMD to triple the L3 cache found on the processor, resulting in significant performance gains in gaming. After months of waiting, AMD is finally bringing the tech to AM5.

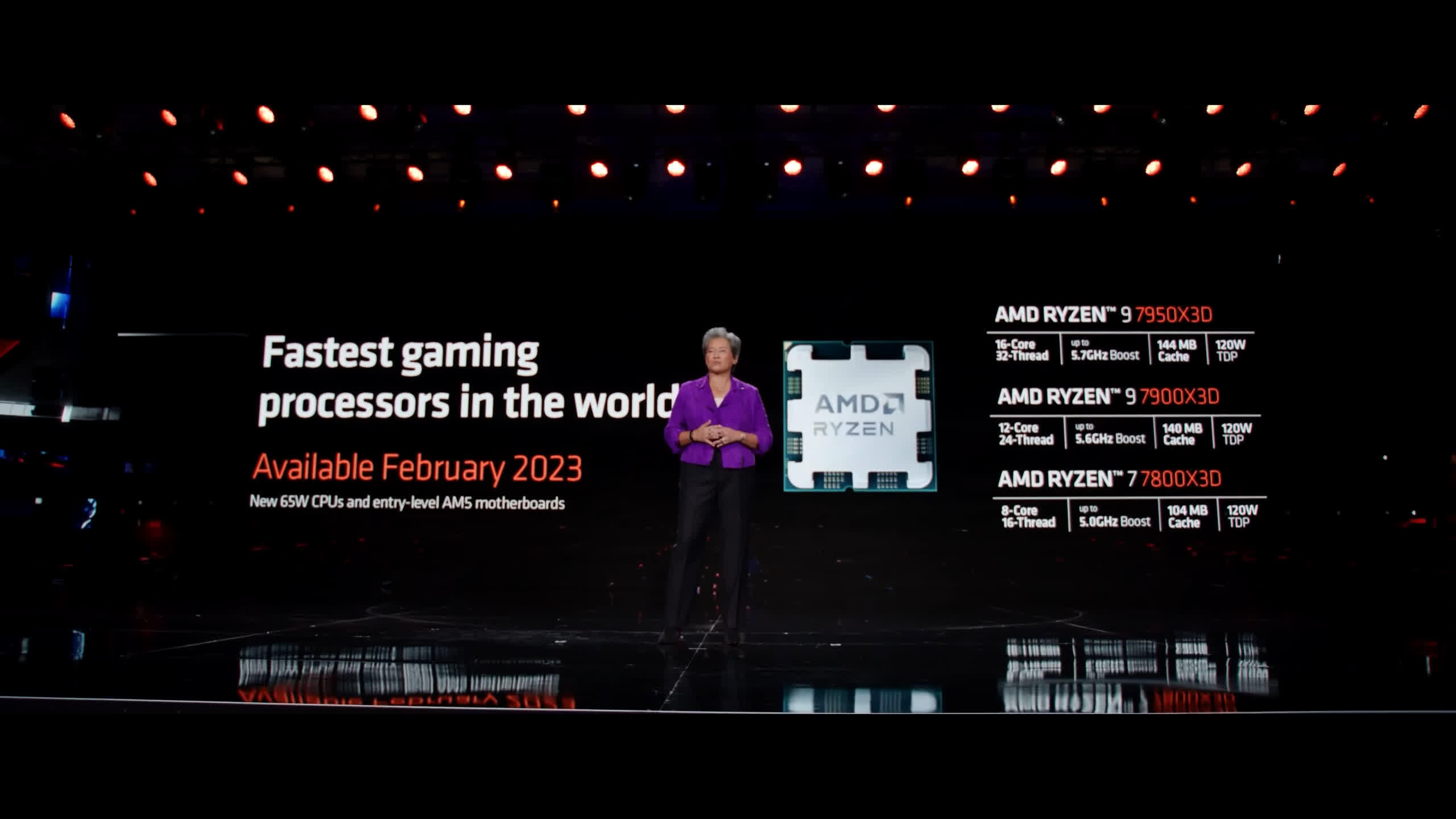

In January, AMD unveiled its first set of Zen 4 X3D processors. While the CES announcement confirmed the specifications featured within the CPUs, AMD did not reveal MSRPs or release dates for the highly anticipated chips. Yesterday, AMD unexpectedly announced those and other details.

First, the 12-core Ryzen 9 7900X3D and 16-core Ryzen 9 7950X3D hit shelves on February 28 for $599 and $699, respectively. Those looking to get their hands on the more-affordable 8-core Ryzen 7 7800X3D will have to exercise patience. It becomes available on April 6 for $449.

While the MSRPs for these processors are relatively close to their non-X3D counterparts, CPUs in the AM5 family have been selling well below anticipated prices. Consumers should expect the new X3D chips to cost anywhere from $100 to $200 more than a processor without the technology.

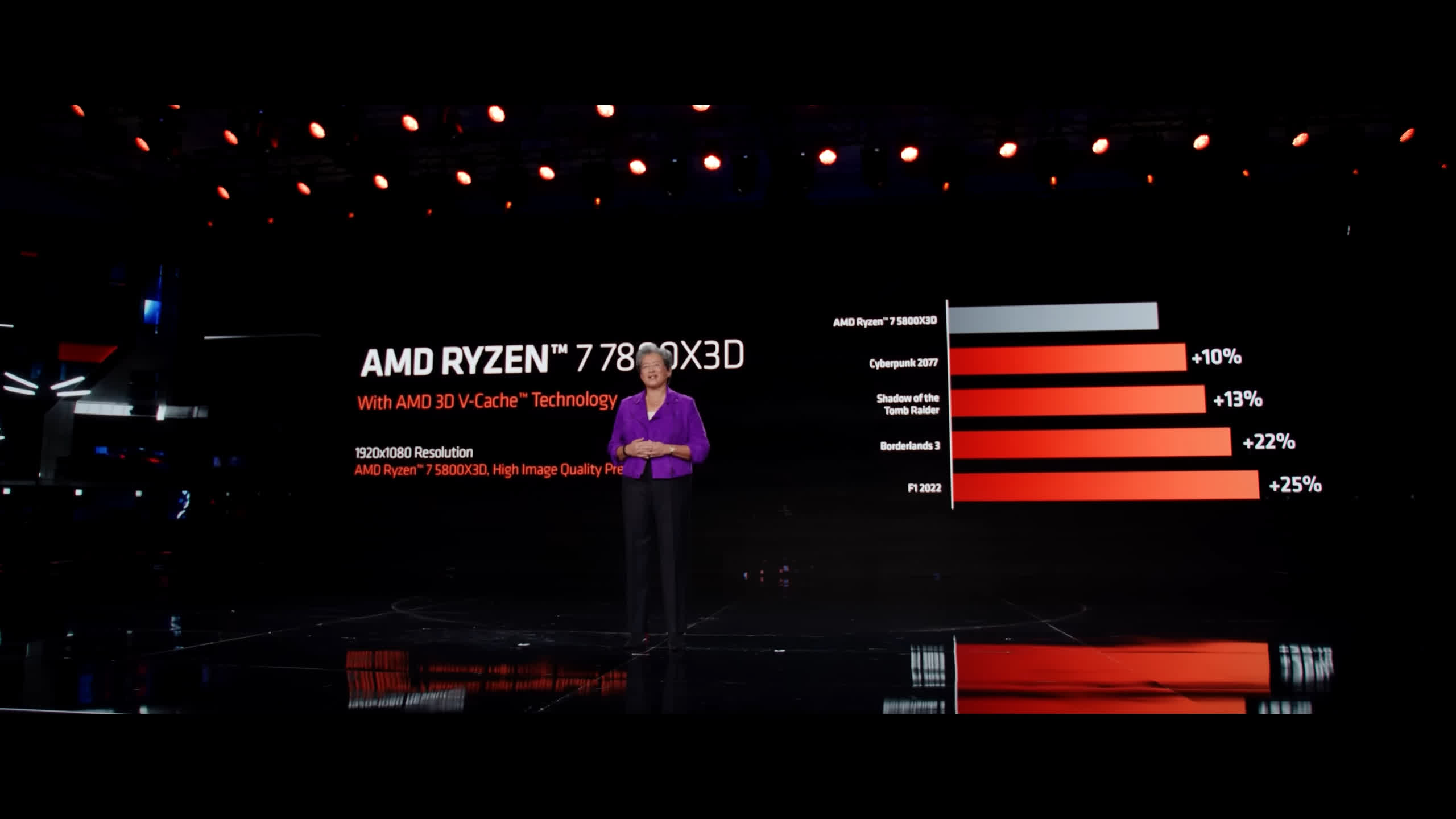

During the CES keynote, AMD claimed that the new 7800X3D could perform up to 25 percent faster in gaming than its Zen 3 counterpart, the Ryzen 7 5800X3D. Furthermore, the highest-end 7950X3D reportedly performs up to 24 percent faster than Intel's Core i9-13900K processor.

The new Ryzen 9 processors with 3D V-Cache may also bridge the gap in productivity tasks that were heavily prevalent on the previous 5800X3D. While that processor struggled in application benchmarks, the 7900X3D and 7950X3D should compete right at the top, with the latter beating the i9-13900K in some tasks by up to 52 percent, according to AMD.

All three X3D processors feature the same 120W base power draw and a maximum of 162W, which is less than both non-X3D Ryzen 9 models. The chiplet cache design featured on the X3D chips causes more heat to be generated at lower wattages, forcing AMD to limit them. Due to the high temperatures, AMD recommends a 280mm liquid cooler as a minimum for the new processors.

Overall, AMD's new processors are an excellent option for gamers. Introducing the Ryzen 9 models also means buyers will no longer need to sacrifice productivity in favor of gaming performance. Just be sure to have an adequate cooler ready for these chips.