Something to look forward to: As CPU core counts continue their upward trend, there's been a pressing need to improve DRAM bandwidth as well. DDR5 SDRAM will quadruple capacity per die and double the effective bandwidth, all while lowering power consumption thanks to architecture refinements.

The JEDEC Solid State Technology Association has announced the final DDR5 memory specification with a series of significant upgrades over the previous standard that is now over six years old and in dire need of a worthy replacement. After all, the standards body took two years more than originally planned to align what's coming next to the growing needs of system manufacturers.

Must read: Anatomy of RAM

The DDR5 SDRAM standard quadruples the density of DDR4, going from 16 Gb per die to 64 Gb. This will allow manufacturers to make DIMMs with capacities going all the way up to 2 TB. In terms of maximum data rate, DDR5 will offer 6.4 Gbps, or double the data rate of DDR4. However, the first modules to hit the consumer market will only be capable of reaching 4.8 Gbps, which is still a significant improvement over the 3.2 Gbps maximum of DDR4.

The power requirements have been lowered as well. The standard operating voltage is 1.1 V on DDR5 versus 1.2 V needed for DDR4. And while that may seem rather small, there are several architectural improvements that will simplify motherboard designs, while retaining the same 288 pin count.

DDR5 SDRAM modules won't be compatible with current DDR4 slots. Individual DIMMs will have to come with an integrated voltage regulator -- JEDEC calls this the "pay as you go" philosophy where manufacturers will only need to purchase as many voltage regulators as the number of DIMMs that are installed in the end systems. It's not entirely clear at this point, but this could also improve yields as well as power consumption, particularly for data center applications.

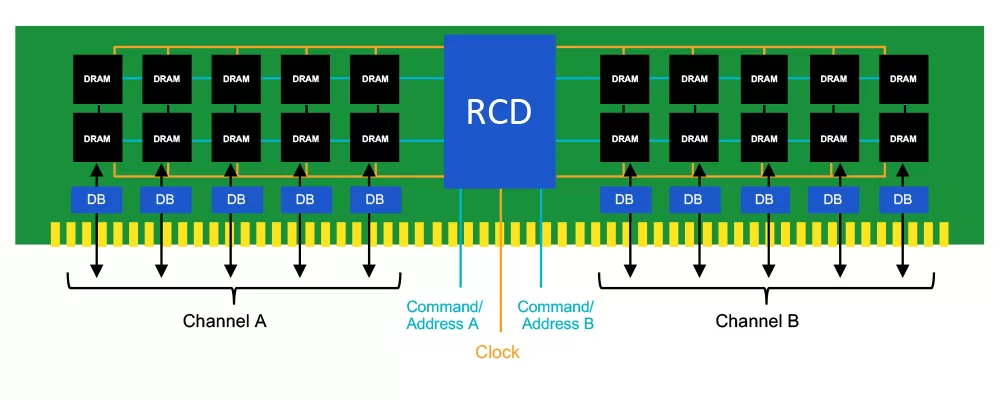

Interestingly, every DDR5 DIMM will work in dual-channel mode by itself, as the memory banks are now addressable on two independent 32-bit sub-channels (40-bit for ECC memory), which is a similar design to GDDR6 and LPDDR4 memory.

Furthermore, the burst length for each of those channels has been increased from 8 bytes (BL8) to 16 bytes (BL16), meaning DDR5 SDRAM will be able to perform two 64 byte operations in the same amount of time it takes for DDR4 SDRAM to perform a single one.

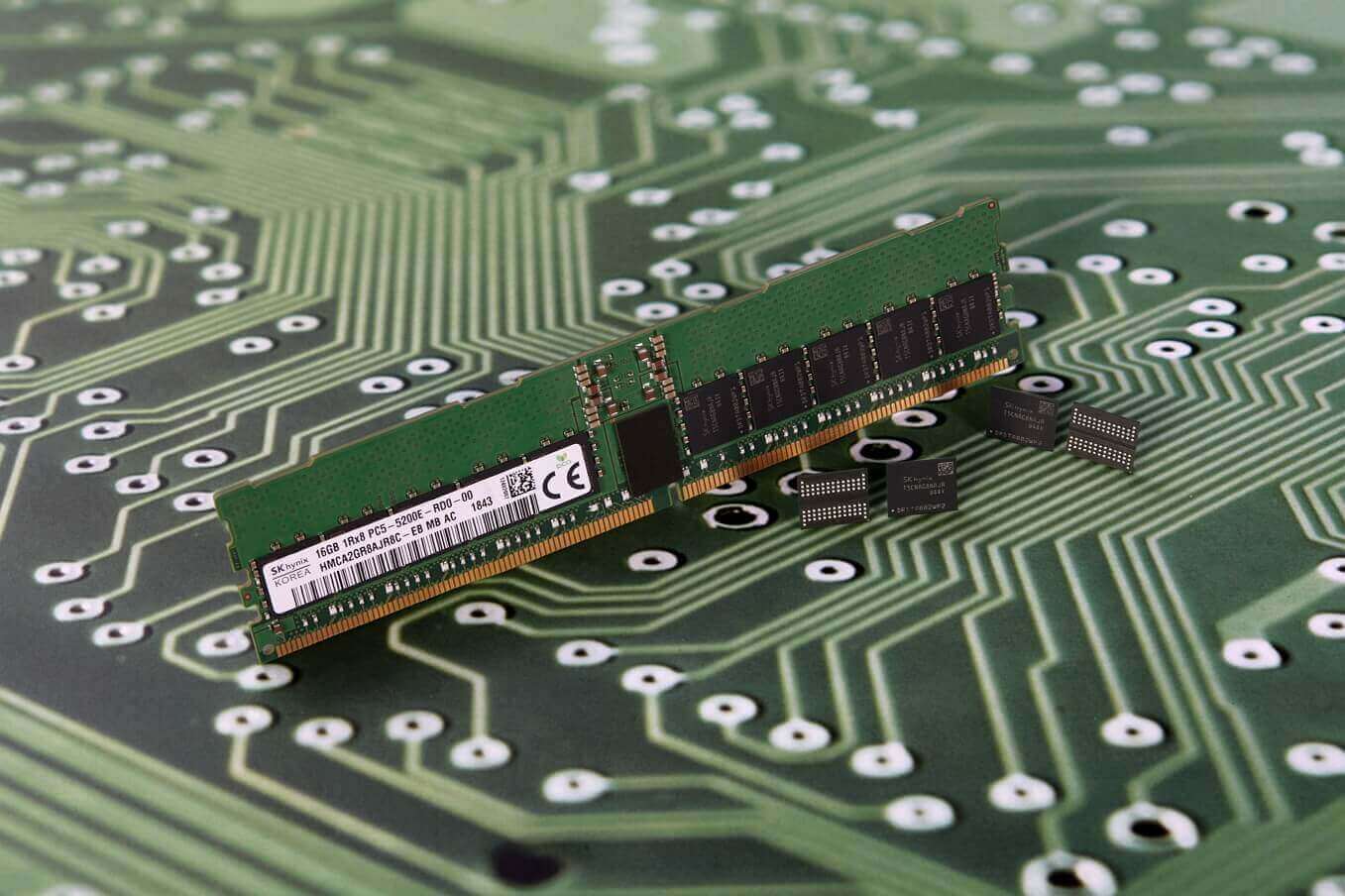

The earliest we can expect to get our hands on platforms with DDR5 support is Q4 2021-Q1 2022. Companies like Micron and SK Hynix are already sampling DDR5 with industry partners and mass manufacturing of DDR5 memory is expected to start later this year.

https://www.techspot.com/news/86000-jedec-releases-ddr5-memory-specification.html