The limit on the core count is more to do with the layout design, that Intel have been following since Skylake, rather than just the process node. Here's a quad core model of that era:

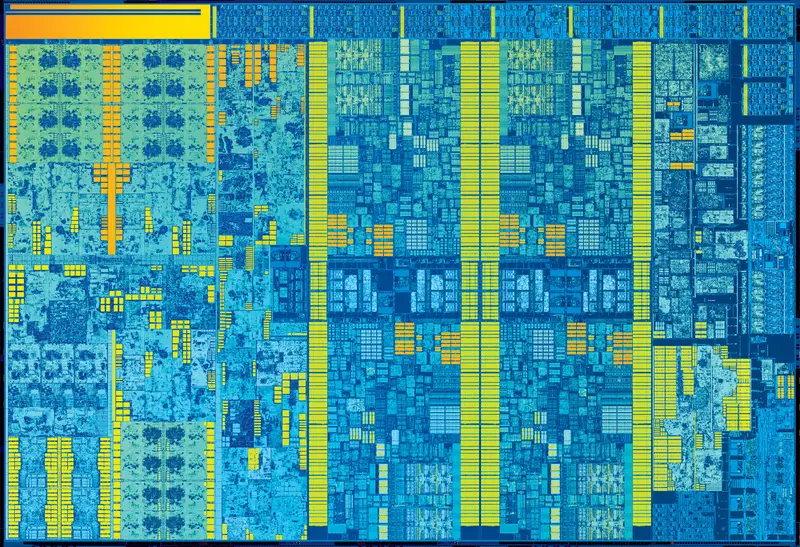

Intel just pack the cores between the GPU (on the left) and the system agent (on the right). This is how that actually pans out in reality:

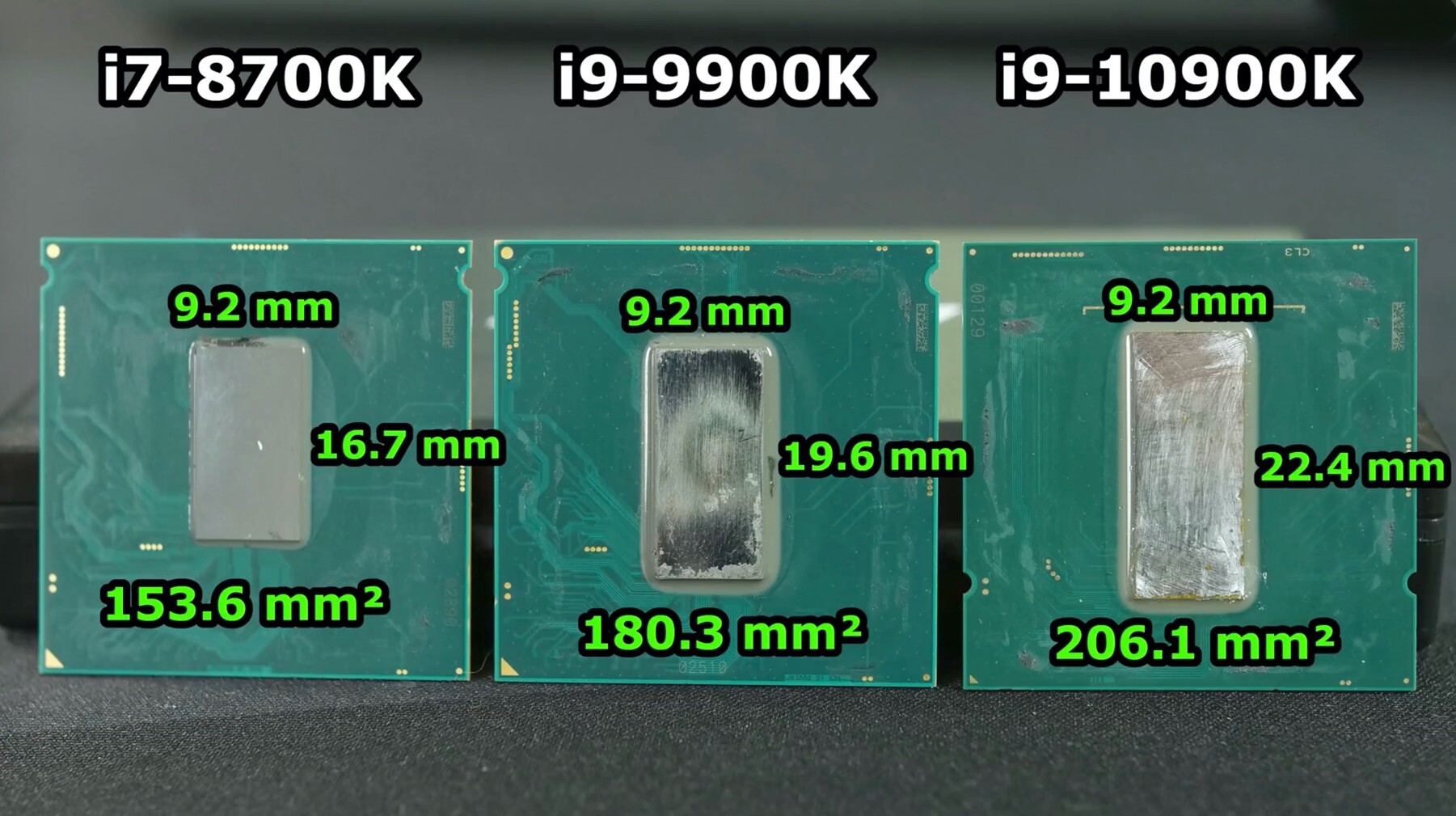

Intel hasn't altered the logic and SRAM density by very much (if any at all) between Coffee Lake and Comet Lake, so we can assume with a reasonable degree of confidence that a core pair adds around 2.5 mm to the height of the die (this can be verified by comparing i5 models to i7/i9 ones, for the respective architecture).

So a 12 core 10900K would be 25 mm tall, a 14 core would be 27.5 and a 16 core (to match a Ryzen full house) would be a ridiculous 30 mm. The package itself is 37.5 mm tall, so that would leave just 3.75 mm above and below the die.

While a die shrink would certainly help here, a full redesign of the chip layout would be better (although the use of the ring interconnect system makes this tricky).

Ring bus makes it hard to raise core count considering that layout. But we must also remember that Cypress cove (Sunny cove) cores are even larger than Skylake cores that also makes power consumption higher and uses even more die space, using 14nm capacity Intel still does not have too much.

Different interconnect (like Mesh used on HEDT/server parts) could solve that problem. It however could create more problems with latencies. And it wouldn't help on power consumption. Intel probably does not have enough capacity either.

Still, we don't know yet how cores are arranged on Cannon lake. I wouldn't be surprised if Cannon lake 8 core is even taller than i9-10900K...