The Peripheral Component Interconnect Special Interest Group (PCI-SIG), the consortium that oversees the popular PCI Express standard, recently published the PCI Express 4.0 (Revision 0.9) specification.

As you may know, the spec is highlighted by the fact that it supports 16 gigatransfers per second (GT/s) data rates - twice as much as today's PCIe 3.0 - and flexible lane width configurations. Best yet, it'll maintain full backward compatibility with the current standard.

Al Yanes, PCI-SIG Chairman and President, said the PCIe 4.0 spec is feature-complete and going through the final IP review. The original timeline was extended, he said, to adhere to their meticulous review process. Despite the delay, he said they are confident that the PCIe architecture is sound for the foreseeable future and ready for the next generation of high-performance bandwidth.

The PCI-SIG notes that members can review and comment on the latest draft specification through August 7, 2017. Feedback can be sent directly to the consortium via e-mail.

The PCI-SIG also announced during its recent developers conference that the next progression in speed for the PCIe 5.0 standard will be 32GT/s. These speeds, the group said, will target high-performance applications such as machine learning, artificial intelligence, gaming, storage, visual computing and networking.

Yanes said the consortium is confident that its 32GT/s bandwidth will surpass industry needs.

Development is already well underway (they're at Revision 0.3) with hopes of completing the specification in 2019.

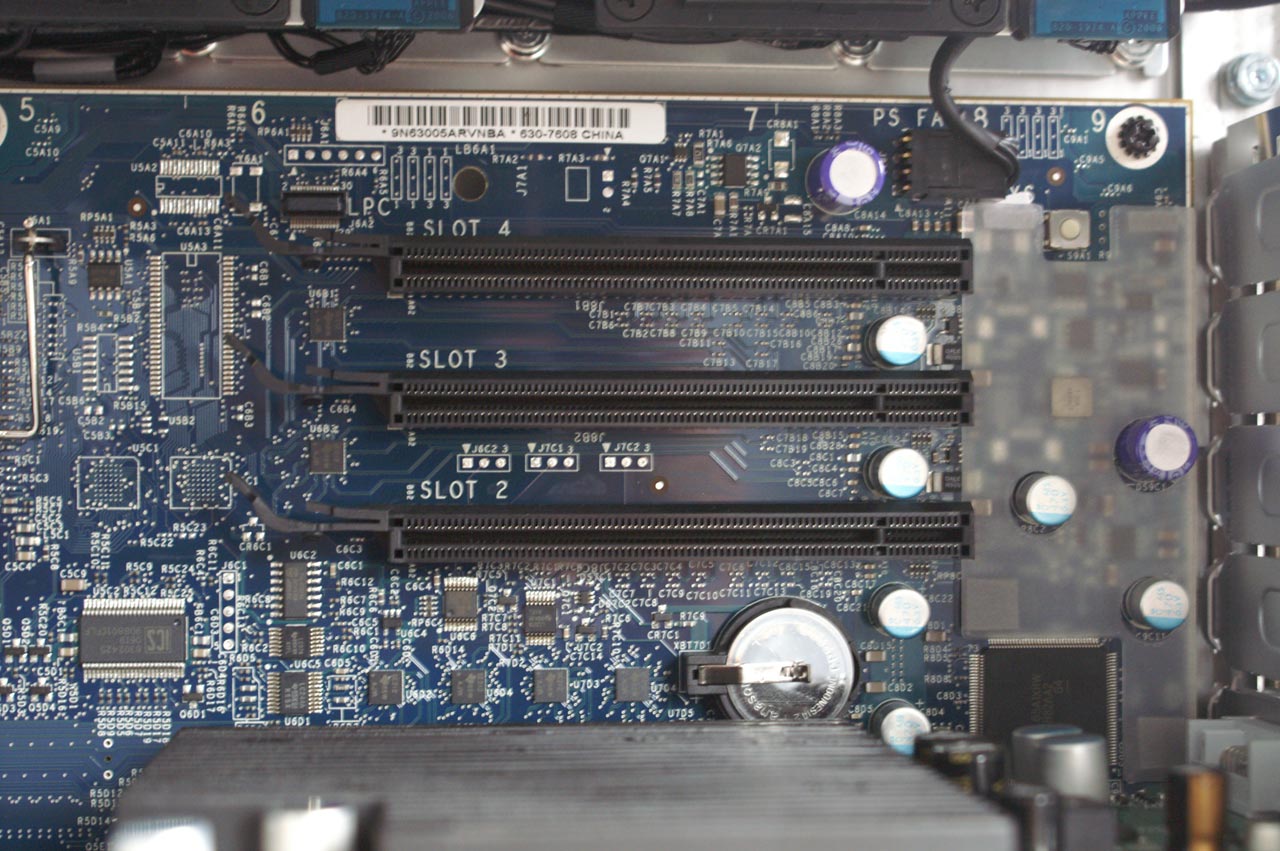

Image courtesy AnandTech