Why it matters: Intel is gearing up for what the company considers the "next major step" in the evolution of the original x86 instruction set architecture (ISA). The Santa Clara corporation is expanding the number of registers for general-purpose x86 operations while introducing a new, all-inclusive vector instruction set based on the renowned AVX-512 ISA.

As explained on Intel's official site for developers, the x86 architecture is now utilized in data centers, personal computers, and various other environments requiring performance-oriented CPUs and heavy computational workloads. Originally introduced in 1978 with the 8086 CPU, the original x86 ISA featured only eight 16-bit general-purpose registers, which were later doubled in number and quadrupled in size.

Registers play a critical role in a CPU, as they store the bits of data the processor actively works on at any given moment. This is why Intel presents the Advanced Performance Extensions (APX) tech as a significant evolutionary step for the x86 ISA. It expands the entire x86 instruction set, granting access to more registers and introducing new features to enhance overall CPU performance.

APX, according to Intel, doubles the number of general-purpose x86 registers from 16 to 32, providing compilers with more space to store data. Compared to a binary program compiled for the "baseline" Intel x64 ISA, the corporation explains, APX-compiled code contains "10% fewer loads and more than 20% fewer stores."

In simple terms, register accesses are faster and consume "significantly less dynamic power" compared to complex load and store operations. This improved efficiency in next-generation Intel CPU models could result in higher performance levels. APX will also expand the conditional instruction set of the x86 ISA, which was first introduced with the Pentium Pro processor with the CMOV/SET instructions.

These instructions are extensively used by today's compilers, and APX seemingly improves the branch prediction capabilities of Intel CPUs. According to Intel, programmers can take advantage of APX features by simply recompiling their code, as no source code changes are expected. APX once again demonstrates the advantage of the "variable-length instruction encodings of x86," with new features enhancing the entire ISA through "only incremental changes" to the underlying silicon for decoding instructions in hardware.

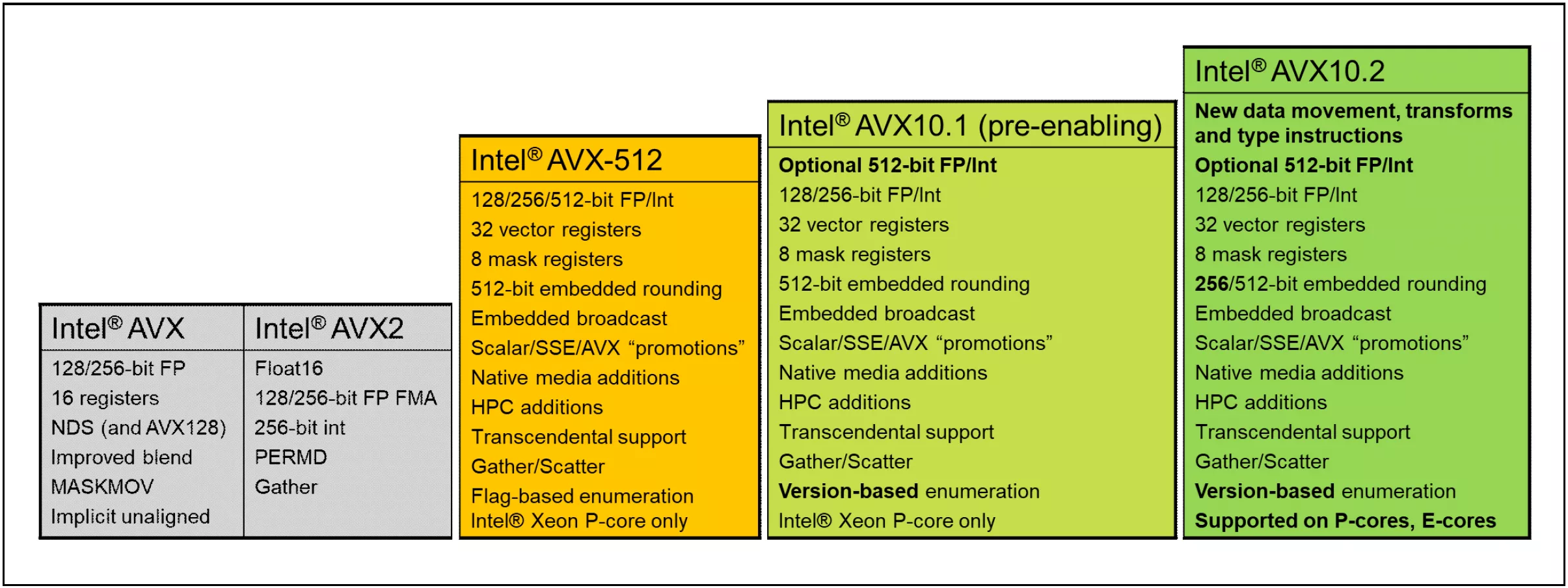

In addition to APX, future Intel CPU generations will include the new AVX10 ISA. This tech, as explained in the official paper, is a new major implementation of the AVX-512 vector instruction set first proposed by Intel in 2013. The new ISA will establish a "common, converged vector instruction set" across all Intel CPU architectures, making it supported on all future processors, including both Performance cores (P-cores) and Efficient cores (E-cores).

Intel initially introduced support for AVX-512 vector instructions on 12th-Gen Core consumer CPUs, but they only worked on P-core units and were later unexpectedly disabled with a firmware microcode update. Among other things, vector extensions to the x86 ISA proved to be extremely popular among developers trying to emulate complex, modern console architectures like the PlayStation 3 (RPCS3).

The AVX10 extension of the x86 ISA will provide support for all previously introduced AVX (vector) instruction extensions, with a maximum vector register length of 256 bits. The initial AVX10 version (AVX10.1) won't include any new instructions; its sole purpose is to ease the transition from AVX-512 to the proper, all-core compatible (P-cores, E-cores) AVX10 implementation known as AVX10.2.

https://www.techspot.com/news/99556-intel-avx10-apx-next-step-x86-instruction-set.html