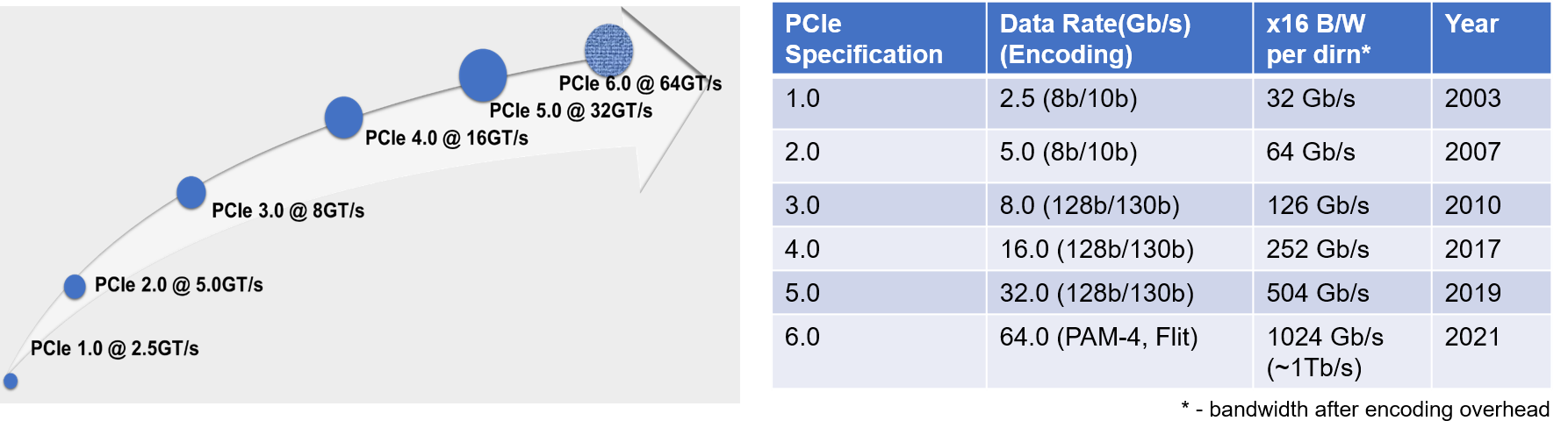

Something to look forward to: While many consumers are still acclimating to the differences between PCIe 3.0 and PCIe 4.0, and PCIe 5.0 SSDs are starting to hit the market, the PCI-SIG consortium this week released the specifications for PCIe 6.0. A long time coming, it has doubled the bandwidth of PCIe 5.0.

The PCI-SIG consortium finally unveiled the full 1.0 specification for PCIe 6.0 this week after going through multiple draft specifications over the previous few years. The last was in October.

The PCIe 6.0 specification will be backward compatible with previous generations. The main benefit is that it doubles the data rate to 64 GT/s and doubles maximum bandwidth to 256 GB/s on x16 lanes compared to PCIe 5.0. Other new features include Pulse Amplitude Modulation with four levels (PAM4), Lightweight Forward Error Correct (FEC), Cyclic Redundancy Check (CRC), and Flow Control Units (Flits).

According to PCI-SIG's FAQ, it is PAM4 that allows the specification to reach such high bandwidth. It modulates signals across four levels, packing two bits of information in a serial channel into the same amount of time.

However, the increased bandwidth leads to a higher bit error rate, which FEC and CRC should help correct. That bandwidth and those features require PCIe 6.0 to switch to Flit mode data exchange.

The latest components in most consumer PCs right now, like graphics cards and SSDs, are still transitioning from PCIe 3.0 to 4.0, and some companies are starting to bring out their first 5.0 SSDs. PCI-SIG says 6.0 will initially target data centers along with industrial, automotive, military, and aerospace applications. It probably won't come to everyday consumers for a while.