Highly anticipated: While there's a Zen 3 announcement inbound, we're getting a few key details ahead of the October announcement thanks to leaked developer documents. While this leak doesn't paint the whole picture for what Zen 3 is going to look like, it suggests it should be another strong CPU series for AMD with lots of generational improvements.

Allegedly confidential documents have been leaked by Twitter user CyberPunkCat that seem to offer details on changes to Zen 3 that will come with the Ryzen 4000 desktop series, code named "Vermeer."

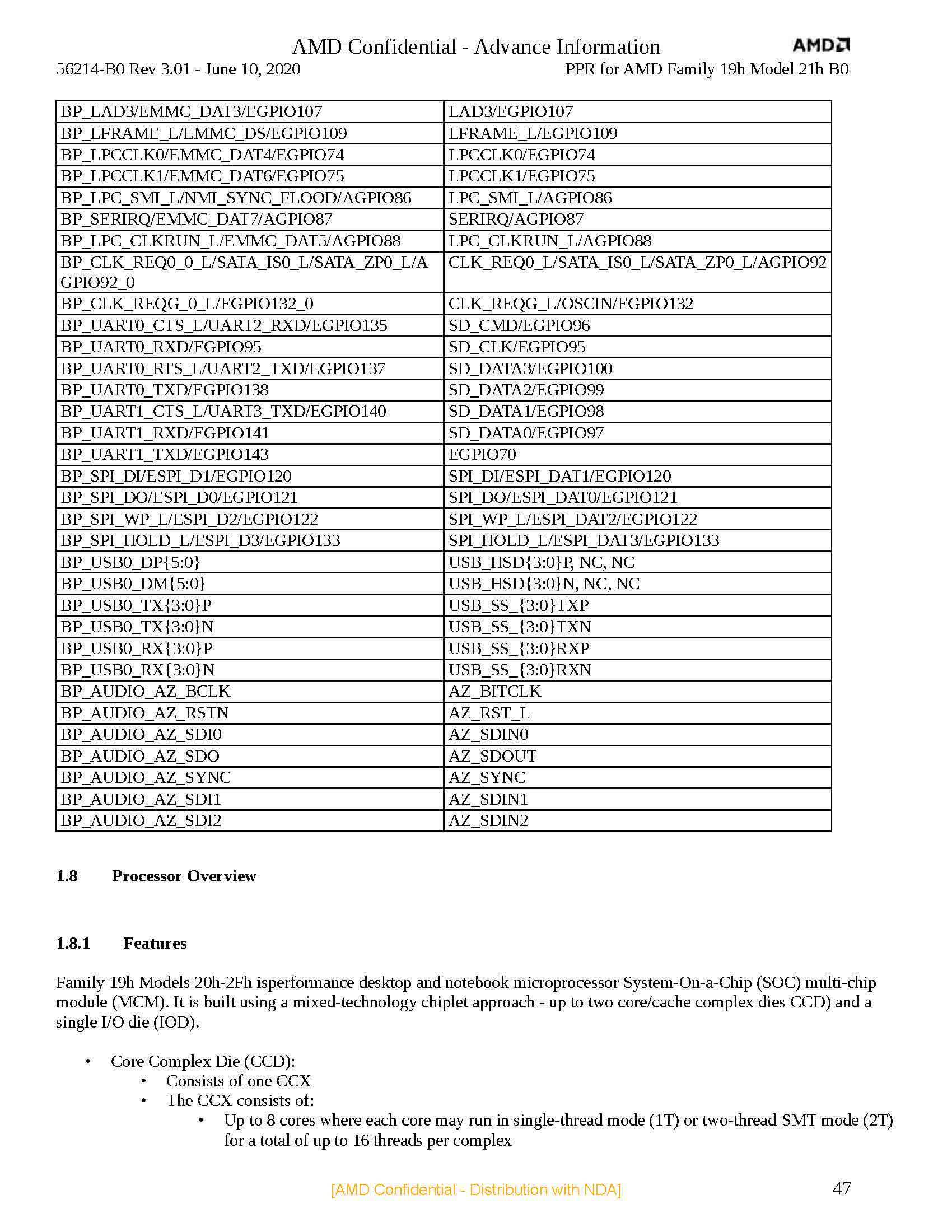

We know that AMD is taking the wraps off of Zen 3 in October, and the details found in the documents reiterate some things we already know, while offering bits of new information. The document appears to be a Processor Programming Reference (PPR) for AMD's Family 19h, Model 21h B0, which would be Zen 3. Previous Zen+ and Zen 2 architectures belong to AMD's Family 17h, with various models and revisions.

AMD usually makes this type of documentation available to developers after launch, so it isn't exactly privileged information. Furthermore, this kind of developer documents tend to be easily circulated -- just ask Intel.

The most notable changes to Zen 3 appear to be happening in the CCD/CCX configuration. Zen 3 will continue to make use of a MCM (multi-chip module), or chiplet design, that will use two CCDs and one I/O die. There will only be one CCX per CCD, and this CCX will consist of eight cores capable of running in either single-thread mode (1T) or two-thread SMT mode (2T). So, that's 16 total threads per CCX.

This may suggest that Zen 3 parts will top out at 16 cores, in the same fashion as the Ryzen 9 3950X. Though, we'll have to wait and see as AMD may well have some tricks up its sleeve.

Furthermore, AMD is reworking its cache subsystem. There will be a total of 32MB of L3 cache (as opposed to 16MB per CCX with Zen 2) shared across all eight cores in the CCX. While Zen 2 offered 32MB of L3 cache per CCD, it had to be shared between two separate complexes. There's also 512KB of L2 cache per core within the CCX, for a total of 4MB of L2 cache per CCD.

Image credit: CyberPunkCat

Interestingly, AMD is also beefing up the Scalable Data Fabric (SDF), which is the communication backbone of Infinity Fabric responsible for the transport of data and coherency between cores, memory controllers, and other I/O elements. The documents note that the SDF can now handle 512GB per DRAM channel. It looks like there could also be some minor changes to the Scalable Control Fabric (SCF), which is the other half of the Infinity Fabric that mainly handles signaling.

Elsewhere, Zen 3 looks to be bulking up the memory interface with two unified memory controllers (UMC), with each supporting one DRAM channel and each channel supporting two DIMMs. There will also be support for DDR4-3200, which was natively supported with Zen 2. It looks like Zen 3 will mostly retain the same features and connectivity for the Fusion Controller Hub (FCH) that were present in Zen 2.

In addition to some generational clock speed bumps, it looks like Zen 3 will further polish AMD's MCM approach, focusing on improving coherence and latency under the hood. We fully expect a measurable IPC improvement over Zen 2 parts as well.

https://www.techspot.com/news/86723-leaked-amd-documents-offer-new-zen-3-details.html