In a nutshell: Western Digital plans to start mass-producing 162-layer BiCS6 3D NAND, which is likely to be used in PCIe 5 SSDs by the end of this year. The company is also working on NAND with 200+ layers meant for datacenter storage, PLC, and ways to bond together multiple 3D NAND wafers to increase the number of layers.

Western Digital, together with partner Kioxia, just gave us a look at their roadmap for the next few years of NAND development. The company plans to introduce its 6th generation BiCS soon, which will feature 162 layers in TLC and QLC configurations.

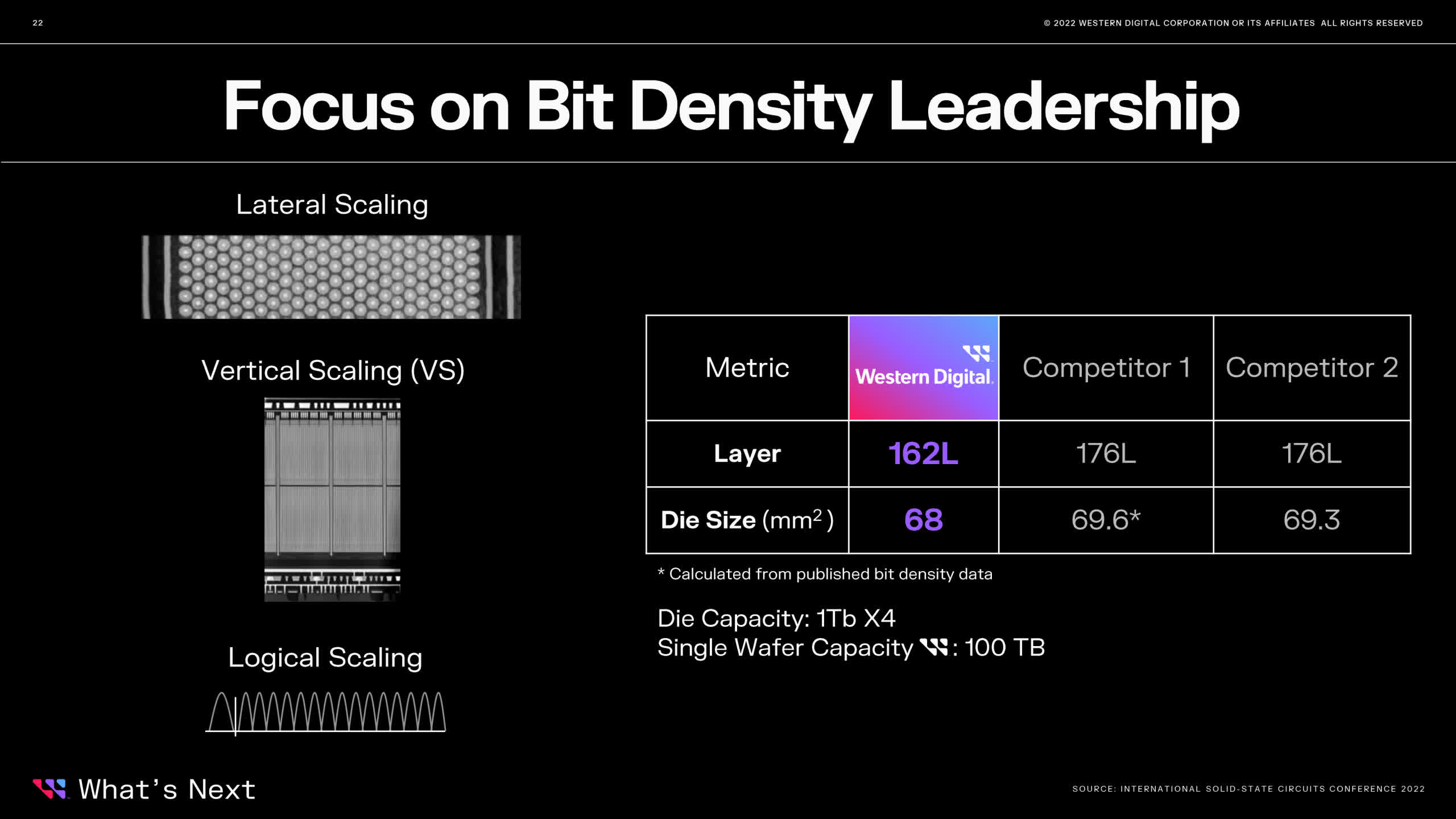

While that might not sound so impressive considering competitors like Micron have had 176-layer NAND for a while now, WD claims they will shrink the memory cell size by using a new material, resulting in smaller die sizes.

The company hopes that this will allow them to build cheaper storage devices that perform just as well. Mass production of BiCS6 3D NAND is scheduled to start in late 2022, with WD planning to use these chips in products ranging from cheap USB drives to PCIe 5.0 SSDs.

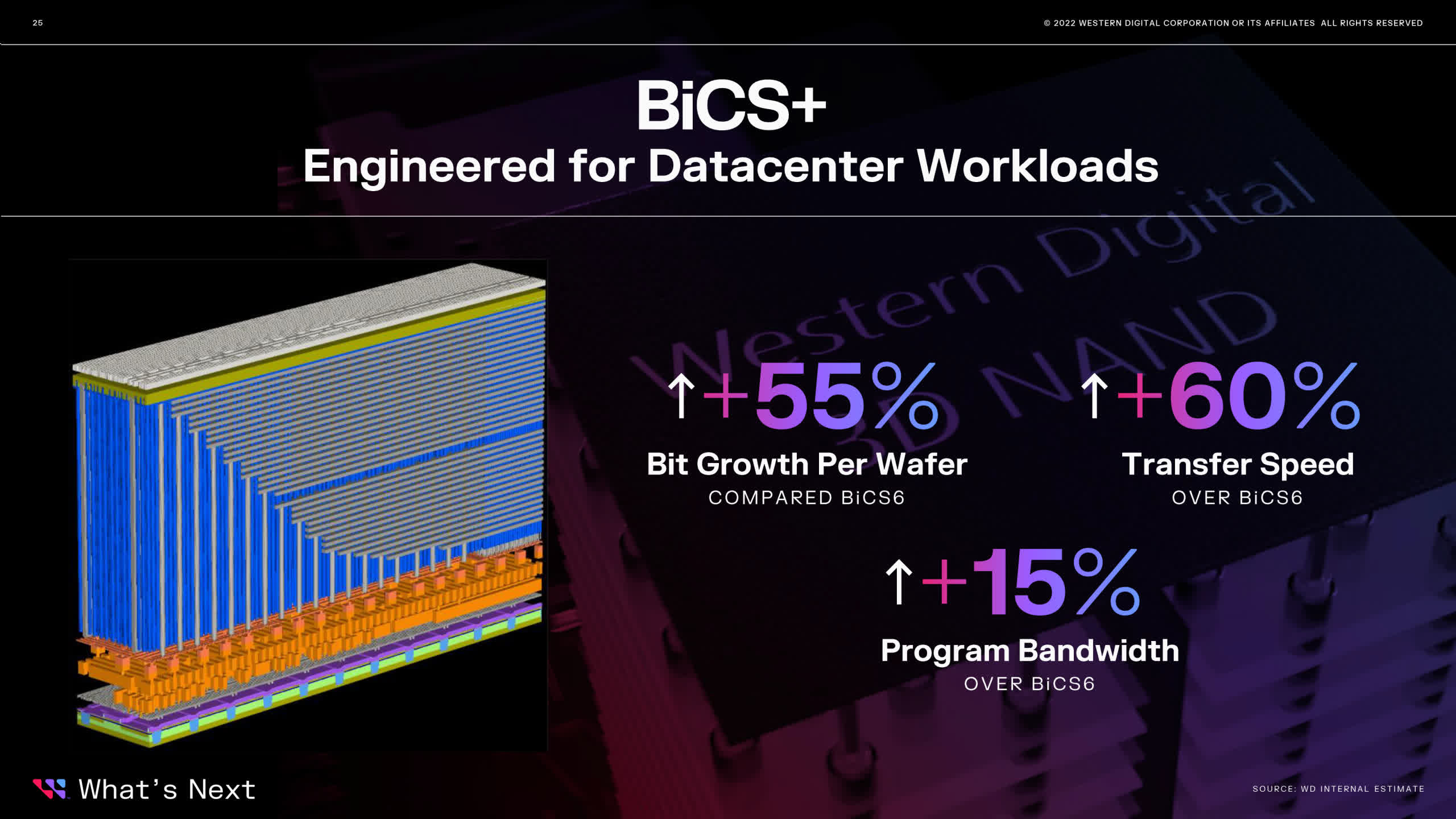

WD also talked about their upcoming BiCS+ memory with over 200 layers, which is set to arrive by 2024. It will feature 55 percent more bits per wafer, 60 percent higher transfer speed, and a 15 percent higher write speed compared to BiCS6.

It's worth noting that BiCS+ is meant to be used only in datacenter SSDs, as the company plans to offer a different class of 2xx-layer NAND for consumer storage, dubbed BiCS-Y.

Western Digital additionally shared that they are working on multiple technologies to improve density and capacity, including PLC, and that they're planning to build NAND with 500+ layers within the next decade.

https://www.techspot.com/news/94592-wd-plans-mass-produce-162-layer-nand-end.html