Why it matters: RISC V pioneer SiFive has gone through several iterations, but has now solidified a business model that essentially positions it as a direct competitor to Arm. If they can continue to execute they will benefit from much of the very healthy RISC V momentum.

We recently attended an analyst briefing with SiFive. We wrote about SiFive last year, and were fairly cautious about the challenges they face. With the benefit of time and a deeper dive into their plans, we came away from this latest meeting much more interested in the company than we had been.

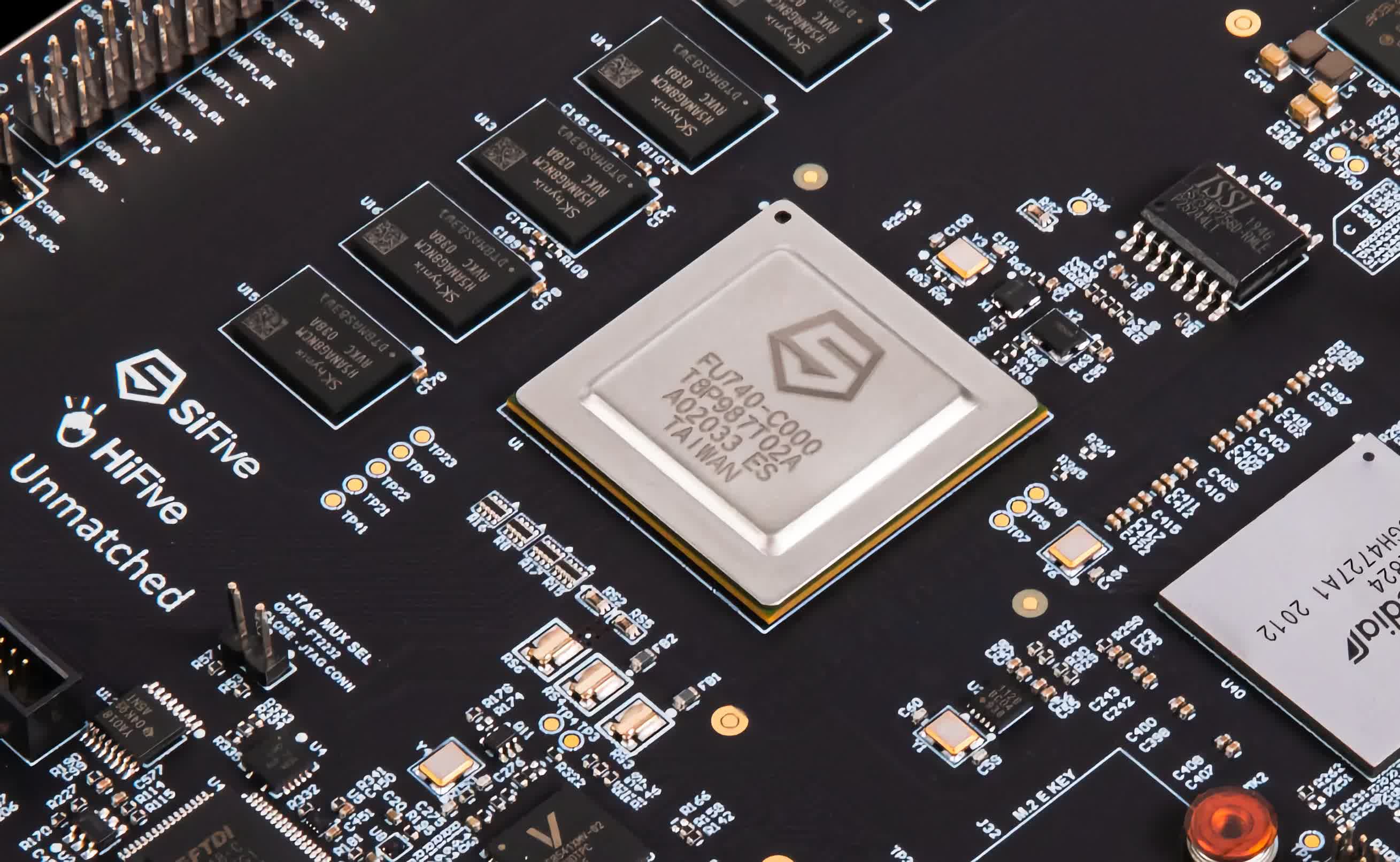

SiFive is one of the leading companies providing RISC V solutions. RISC V is an "open" alternative to the Arm or x86 instruction set architectures (ISA), which power the math inside of processors. We have already touched on the subject of RISC V, it is technically interesting and has arrived at a good time with considerable interest from the market.

SiFive is often described as the "Red Hat" of RISC V, the leading company in commercializing an open source codebase. But this is a flawed description.

SiFive is often described as the "Red Hat" of RISC V, the leading company in commercializing an open source codebase. But this is a flawed description. Instead, we should start to think of SiFive as essentially a direct competitor of Arm, a licensor of ISA intellectual property. They sell "blueprints" that other companies pay to copy into their own chip designs. This seems a bit counter-intuitive since RISC V is "free" and "open."

Editor's Note:

Guest author Jonathan Goldberg is the founder of D2D Advisory, a multi-functional consulting firm. Jonathan has developed growth strategies and alliances for companies in the mobile, networking, gaming, and software industries.

The simple explanation is that there is a big gap between having RISC V code and actually making that into a functioning chip – there are all kinds of add-ons, tools and features needed to bridge that gap, and SiFive, like Arm, makes money by selling those. The more complex explanation is that RISC V is not really "open source," it is better thought of as an "open standard," akin to Wi-Fi.

This is more accurate, but also confusing, hence all the quotation marks around the word "open." Suffice to say that building RISC V chips is not easy and SiFive has positioned itself to solve that problem.

In our defense, we can be forgiven for getting this all muddled in the past, SiFive has undergone several iterations to reach its current model. Prior management had pushed the company in multiple directions including selling their own chips. The new model looks much more coherent and sustainable.

In general, we think RISC V looks to be in fairly good shape. It has won widespread adoption in China driven in part by the low cost of use and in part by geopolitical concerns. And major global chip companies are all adopting RISC V, driven in no small part by questions about Arm's changing business model, and the fact that they are suing one of their largest customers, Qualcomm.

RISC V still faces numerous challenges, not least the by-definition fragmented nature of its "open" roots. That being said, it has gained real traction in many markets including IoT, industrial and embedded systems. There is an argument that RISC V has considerable appeal in Edge AI inference (a massive market to-be), and a non-zero chance that RISC V gains a real foothold in the data center.

And of course, the massive automotive semis market that lies just over the horizon is as open to RISC V as it is to everyone else.

This should mean good business for SiFive. As more companies build RISC V solutions, the appeal of working with a company like SiFive is considerable, especially for non-semis companies building their own chips.

We know many companies, large and small, chip designers and non-chip designers, working with SiFive to accelerate their plans. In some future post we can lay out the advantages of working with SiFive instead of flying solo. Put simply, SiFive should grow with the RISC V market, and that market is growing nicely.

SiFive has customers across industry verticals and end-user markets which is important as RISC V usage is still very much in experimental mode.

At the very least, we think the future of most large chips will entail multi-ISA SoCs, with RISC V/SiFive cores sitting next to Arm cores, and even next to x86 cores. There is another, stronger case that holds that RISC V can end up becoming the dominant ISA in many major markets. We are not ready to go there yet, but we are optimistic about RISC V's prospects and that should benefit SiFive, especially if they can extend their current execution track record.