In a nutshell: In his keynote at ISC 2025, AMD CTO Mark Papermaster emphasized that the next wave of supercomputers will demand breakthroughs in efficiency, reliability, and adaptability, not just raw performance. He noted that industry leaders are now grappling with the realities of explosive growth and the increasingly complex challenges it brings.

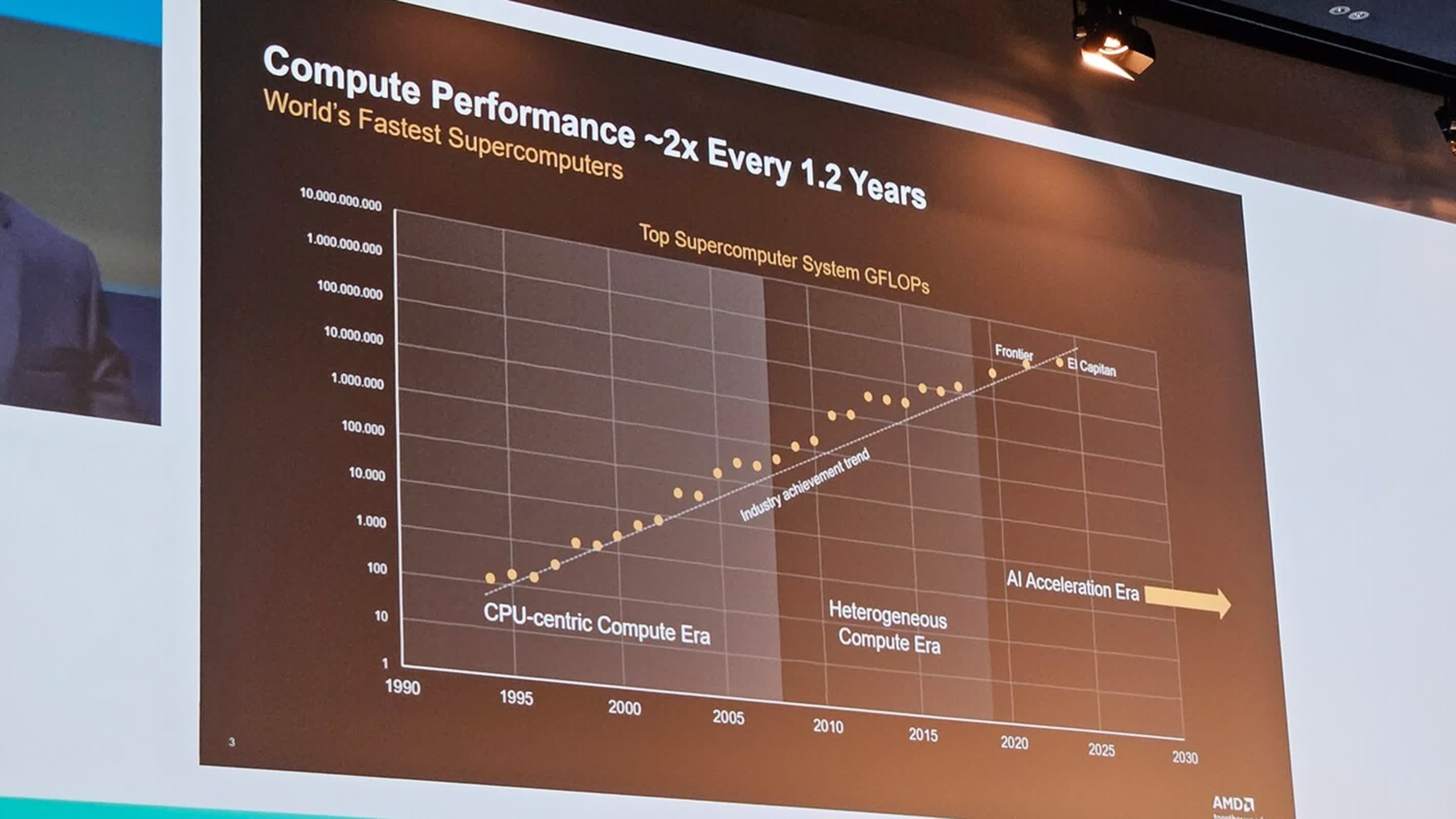

Papermaster began by highlighting the continued surge in demand for high-performance computing, driven primarily by artificial intelligence. He pointed to the emergence of new systems in Germany – such as Jupiter and Blue Lion – as evidence of the sector's rapid expansion. "The performance of supercomputers will continue to increase rapidly," he said, emphasizing that it is user demand that fuels innovation and progress.

While AI remains at the forefront, Papermaster stressed that traditional computing techniques are still essential, especially in scientific applications where precision is critical. He explained that double-precision (FP64) calculations remain vital, and although lower-precision formats like FP16 and FP8 are becoming more popular for certain workloads, a hybrid approach is necessary. "It's not just FLOPS!" he said, underscoring that raw compute power is only part of the equation.

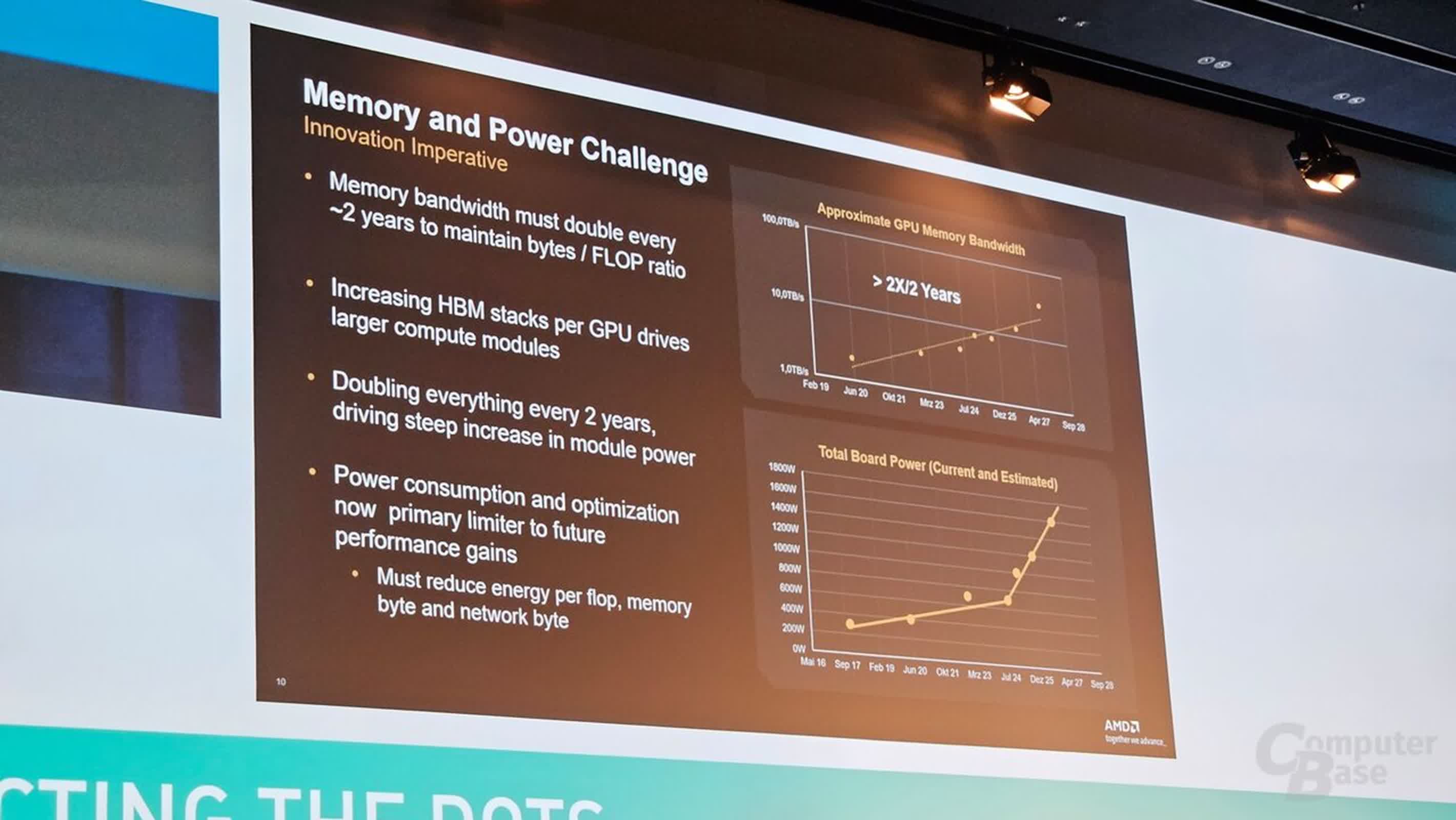

The conversation soon turned to the practical challenges facing the industry. Papermaster noted that while computational performance can, in theory, scale rapidly, real-world constraints such as bandwidth and power consumption are becoming increasingly critical.

He warned that the total board power of accelerators is projected to reach 1,600 watts or more by 2026 or 2027, with 2,000 watts potentially on the horizon.

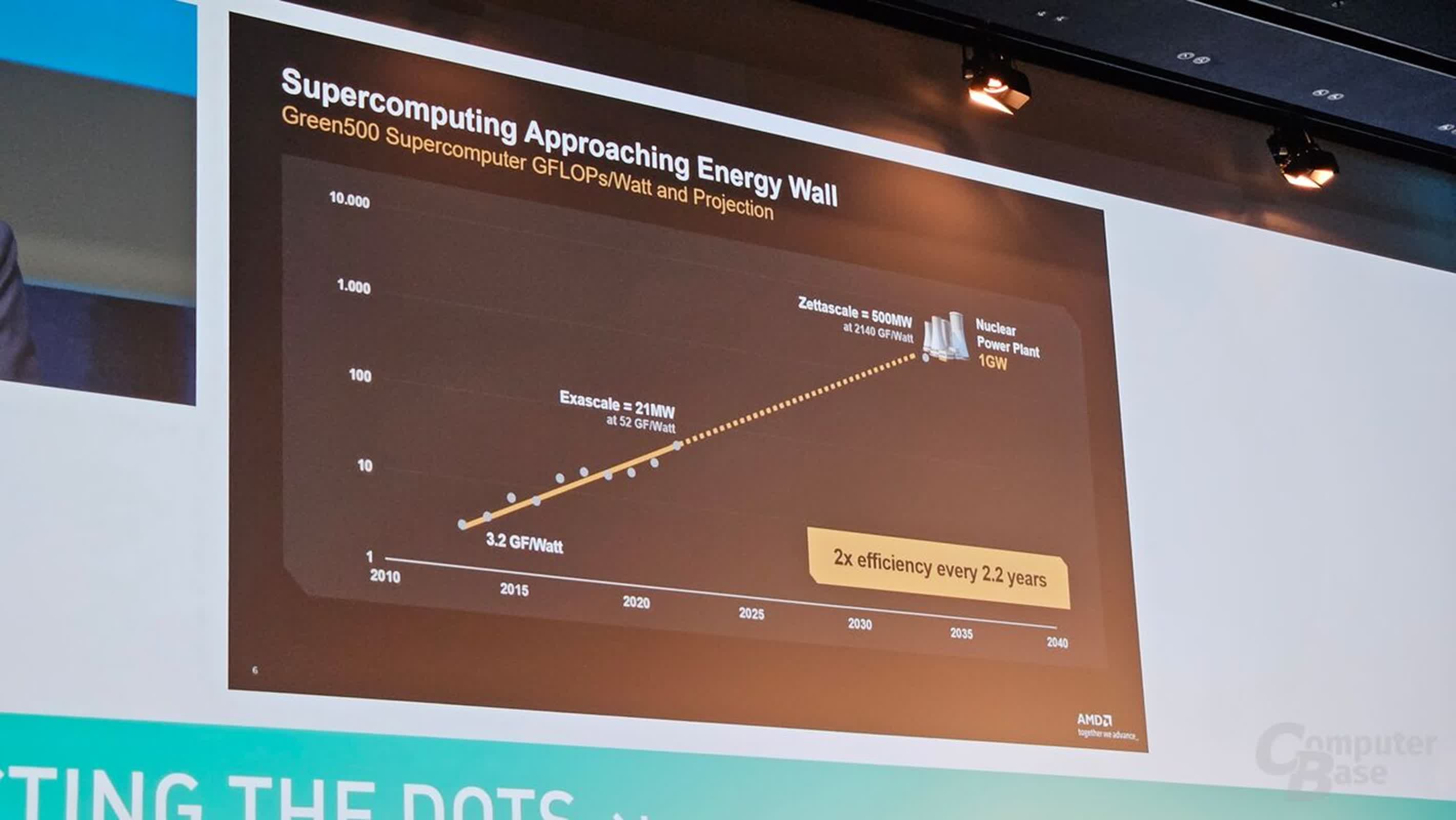

"Power and cooling will be, and in some cases already are, the biggest limitations," he said, adding that memory bandwidth must double every two years to keep pace, which only compounds power demands.

Papermaster noted that future AI data centers could consume power on the scale of hundreds of megawatts. He even joked about the possibility of "15 manufacturers of small nuclear reactors," a tongue-in-cheek reference to the industry's surging energy demands.

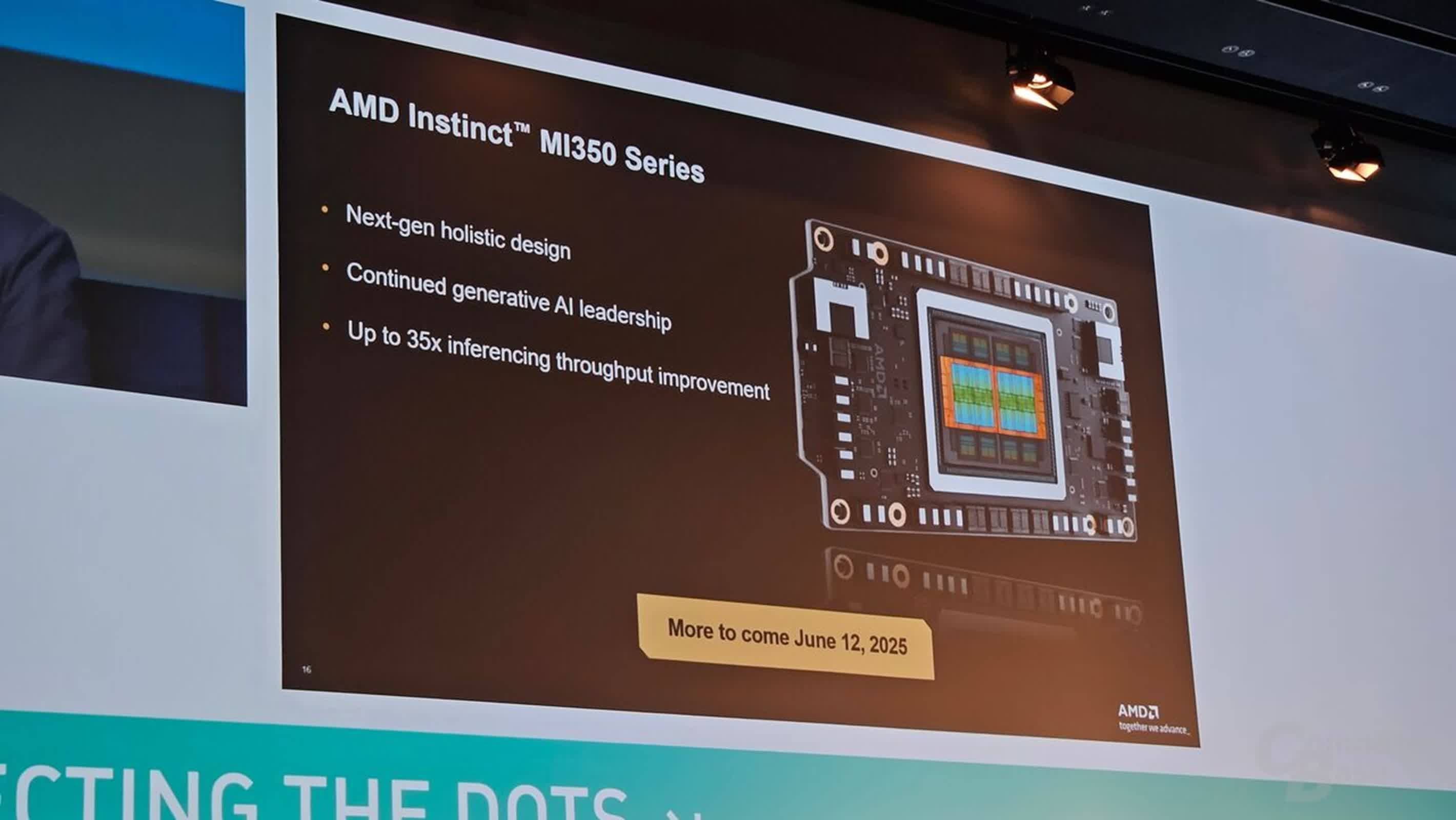

On the product front, Papermaster highlighted AMD's growing momentum with its Instinct accelerators. The MI300X and MI300A have already gained traction, generating $5 billion in their first year and capturing five percent of the market.

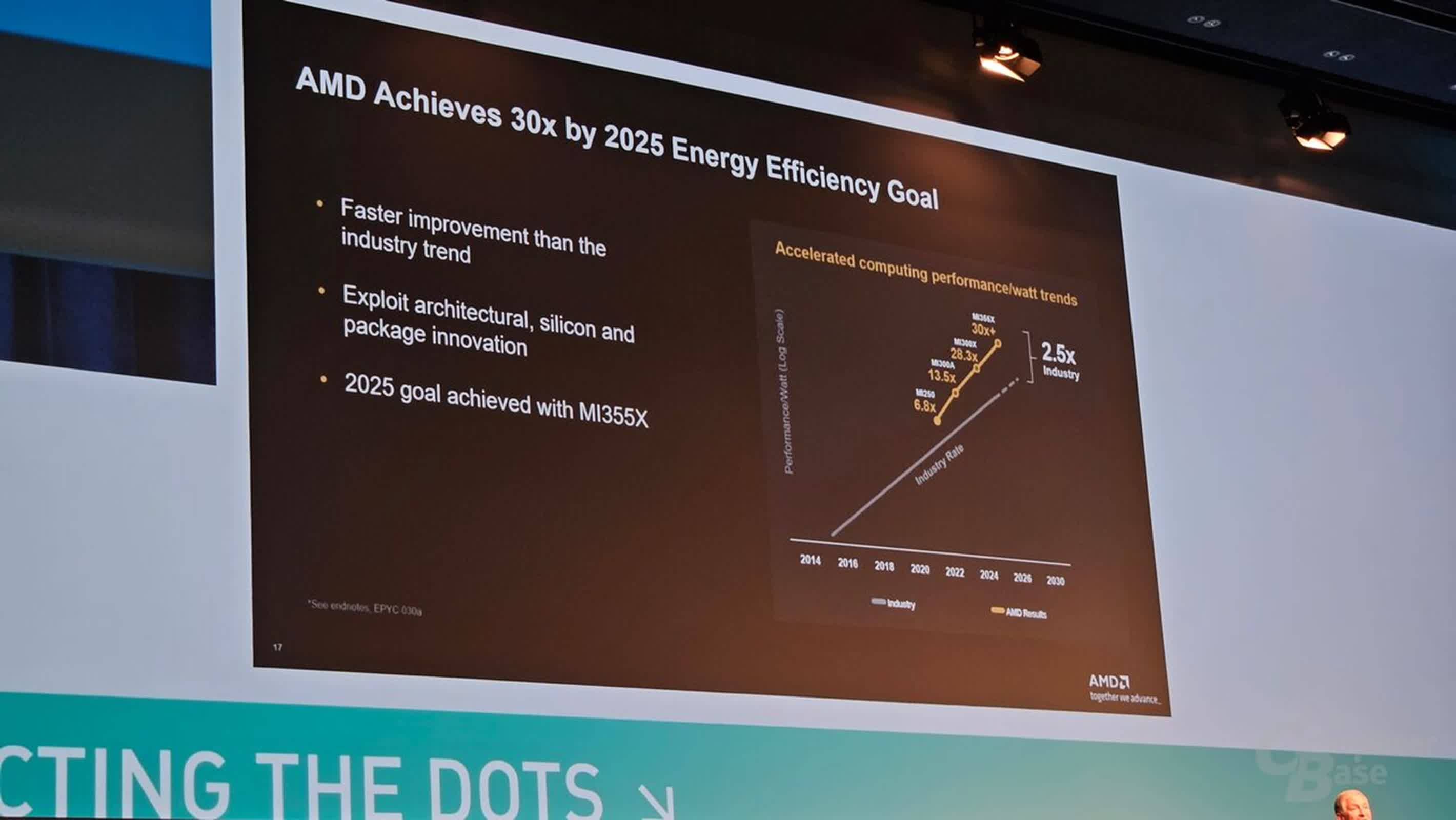

Looking ahead, he confirmed the upcoming launch of the MI355X, which will offer up to 35 times the inference performance of its predecessor in certain workloads. The new accelerator will be available in both air- and water-cooled variants, underscoring AMD's continued focus on performance and efficiency. Papermaster also touched on the potential of in-memory computing as a future leap in energy efficiency, confirming that AMD is actively exploring the technology.

Cost remains a critical concern for professional users, Papermaster acknowledged, as organizations must weigh the trade-off between significant upfront investment and the ongoing expense of extended system runtimes. While AMD continues to support open-source and freely available tools, he admitted that development of their new 2nm chip was "not open – and extremely expensive," requiring significantly more time and resources than previous designs. Many of the tools needed for such advanced chips are proprietary and will likely remain so for the foreseeable future.

On the topic of connectivity, Papermaster pointed to "Ultra Ethernet" as a promising technology that could help lower infrastructure costs. He noted that Nvidia, feeling the competitive pressure, has begun opening up its NVLink interconnect to other vendors in response – an effort to counter Ultra Ethernet's disruptive potential. A wider array of options in this space, he suggested, could ultimately help drive down costs and foster a more competitive ecosystem.

When asked about the role of RISC-V, Papermaster clarified that while AMD is already using RISC-V in certain applications, it is "currently unrealistic to classify these chips as supercomputers." He emphasized that RISC-V remains in its early stages of maturity and will require substantial development before it can compete at the highest performance tiers.

Looking ahead, Papermaster envisioned the ideal supercomputer as a highly versatile system capable of handling a broad spectrum of workloads. He acknowledged that this goal remains a long-term aspiration, and that specialized architectures will continue to dominate for the foreseeable future. However, modular construction – exemplified by projects like Jupiter – provides a promising path forward.

Future supercomputers are likely to be assembled from many interconnected components, each optimized for specific tasks. Achieving high performance across such diverse workloads, he said, will require a blend of emerging technologies, including optical interconnects and eventual support for quantum computing.

Image credit: ComputerBase