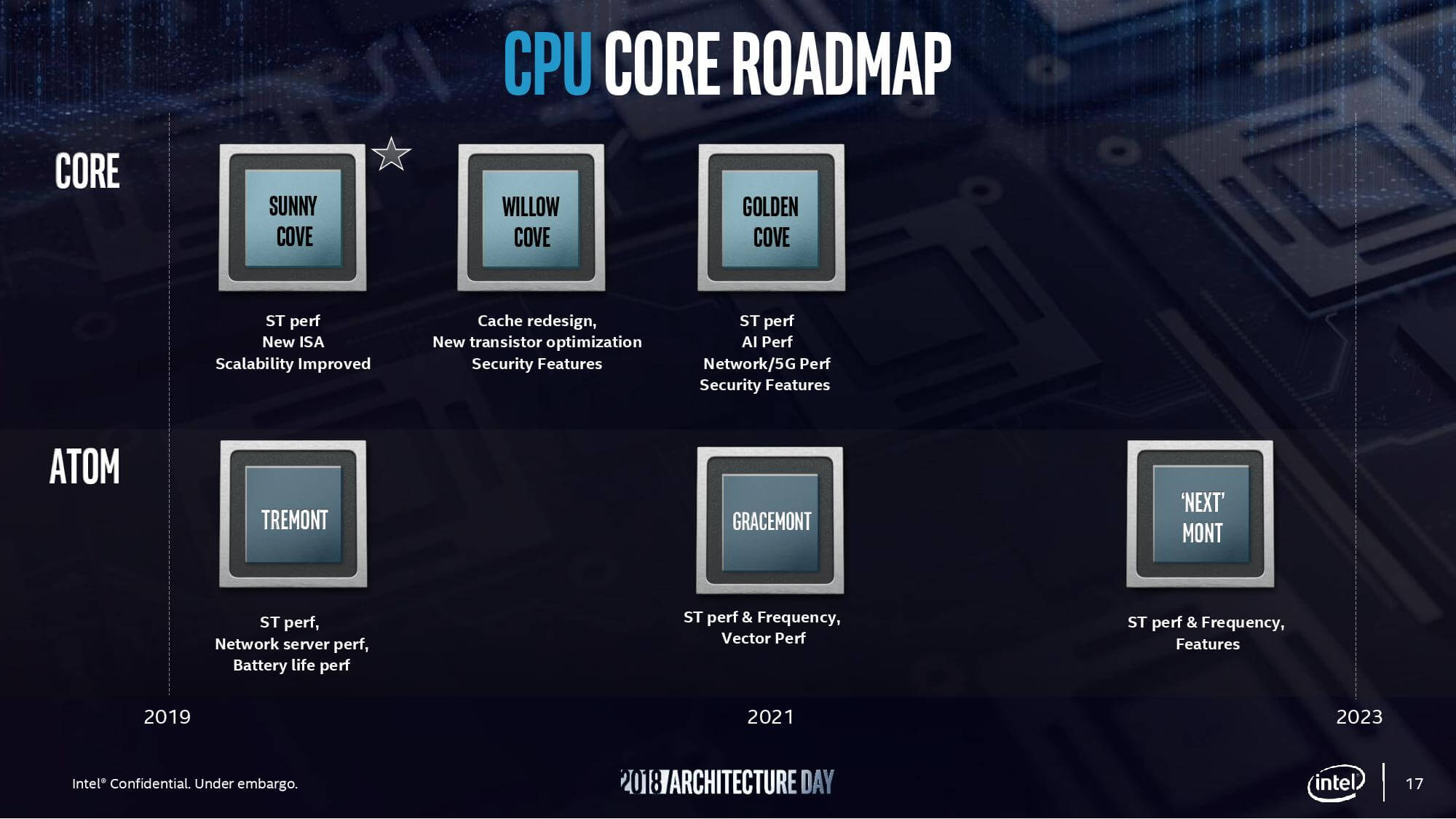

Something to look forward to: For the first time in several years, Intel is going to improve the instructions per clock performance of its CPU lineup. Architecture changes allow for more parallel instructions to be executed per cycle, but single-threaded tasks will also become faster across the board.

Looking ahead to 2019, Intel has revealed its plans for Sunny Cove architecture. The next-generation CPU will be built on a 10nm process and is designed to focus improving instruction execution parallelization as well as efficiency. Both Intel Xeon and Intel Core series processors will be making use of Sunny Cove.

To improve performance, Sunny Cove brings support for AVX-512 instructions. Accelerated vector operations will speed up neural networks as well as help with encryption and compression. Up to 75 percent more performance can be expected in these specific workloads.

Attempting to handle more instructions per clock cycle requires more cache space. First level caches has been expanded by 50 percent. Second level cache has also been expanded by 50 percent, but will vary based on the target market of specific CPUs.

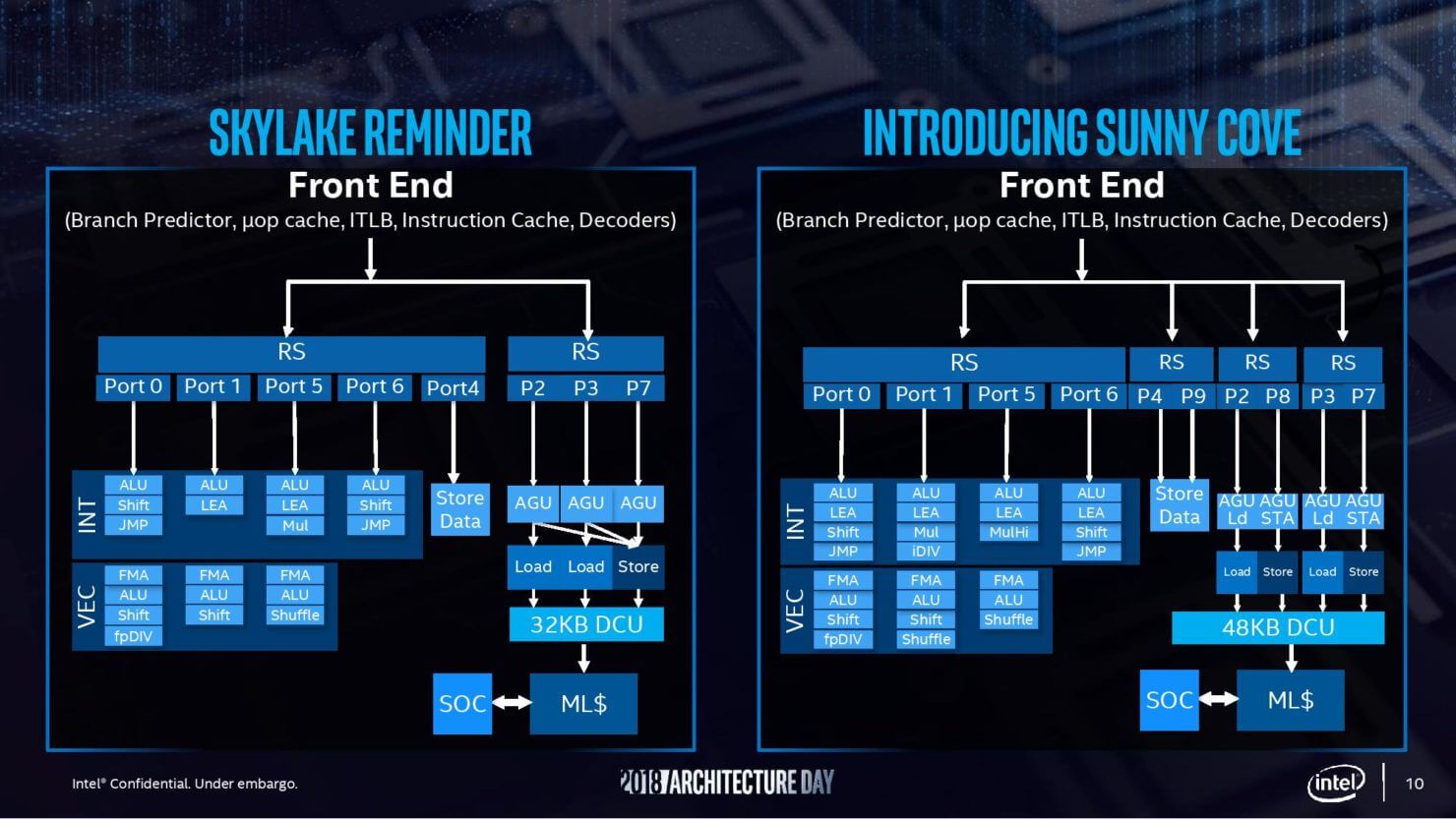

To further improve parallel execution, Intel has added additional reservation stations that pass along instructions, doubling the number from two to four. Now up to five instructions can be sent per cycle as opposed to four on Skylake. Extra execution units have also been added for LEA instructions and vector shuffling.

Skylake CPUs can manage two loads and one store operation per clock cycle, while Sunny Cove architecture will be able to handle two loads and two stores. Scheduling of out-of-order executions will be much more flexible as a result of being able to run more memory operations per cycle.

Perhaps one of the greatest changes comes as a result of memory addressing. Both AMD and Intel switched to 64-bit addresses back in 2003, but only 48 bits have been used. Now, more significant bits are being put to work. Up to 4PB of memory is possible via 52-bit addresses. Virtual memory addresses expand up to 57 usable bits, allowing for 128PB. For high end consumer CPUs, this is completely unusable, but enterprise users with deep pockets will certainly find a way to take advantage of the new capabilities.

Consumer CPUs carrying the Intel Core branding using Sunny Cove architecture are expected to become available during the second half of 2019. On the enterprise front, Intel has not directly given a clear answer. Intel will be offering Cascade Lake in the first half of 2019 followed up by Cooper Lake, but Sunny Cove may not be realized until it carries Ice Lake nomenclature for Xeon processors.