Why it matters: The X280 is a new RISC-V CPU being developed to survive the harsh conditions of outer space and let NASA scientists accomplish their next missions. Expectations are high: at least a 100x increase in computing power, while keeping the same energy consumption.

NASA will soon perform a significant upgrade to the systems employed in its spaceflight computers, adopting the RISC-V architecture developed and provided under open-source licenses. NASA selected SiFive to provide the CPU cores, a fitting choice as the company headquartered in San Mateo, California was founded 7 years ago to develop RISC-V based hardware (where "V" indicates this is the fifth generation RISC instruction set) and put compatible processors on the market.

SiFive is a fabless chip company, so actual production of the chips will be in the hands of Microchip Technology, a company based in Chandler, Arizona specialized in manufacturing microcontrollers, EEPROM chips, and other IC products.

NASA awarded a $50 million contract to the two companies, expecting the final delivery of the new X280 CPU in a 3-year timeframe. X280 will be the computational foundation of the High Performance Spaceflight Computing (HPSC) project, NASA's initiative to design and develop new spaceflight technology capable of providing "at least" 100 times the computational capability of currently employed systems, while using the same amount of energy.

X280 will replace the RAD750 processor, an aging PowerPC-based CPU manufactured by BAE Systems and employed in several NASA missions since 2005. The Mars Perseverance rover and the recently launched James Webb telescope are two of the most celebrated space endeavours made possible by the RAD750 CPU.

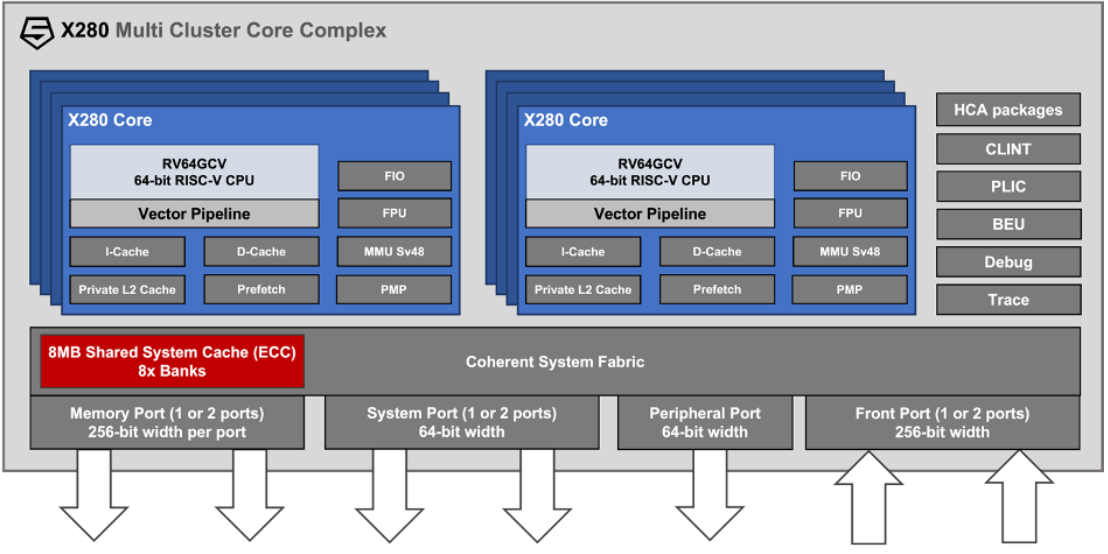

The X280 CPU currently in development for the HPSC system will utilize 8 SiFive Intelligence RISC-V vector cores with 4 additional cores, which will provide the computational capability jump NASA is projecting before retiring today's space computers. According to SiFive, the massive increase in performance will help usher in new possibilities for autonomous rovers, vision processing, space flight, guidance systems, communication, and other mission elements in space exploration.

Another paramount feature of the X280 will be its tolerance to radiation: HPSC will be specially designed to survive the harsh and hostile space environment, controlling many space activities with no possible aid from Earth and ensuring its ability to operate and provide reliable results for most critical operations.

https://www.techspot.com/news/95911-sifive-risc-v-cores-microchip-processors-power-nasa.html