In brief: Taiwan Semiconductor Manufacturing Company (TSMC) during its worldwide technology symposium this week shared additional information regarding its upcoming 3nm N3 node. It's still a ways out but fortunately, TSMC has plenty of other tech to fill the gap between now and then.

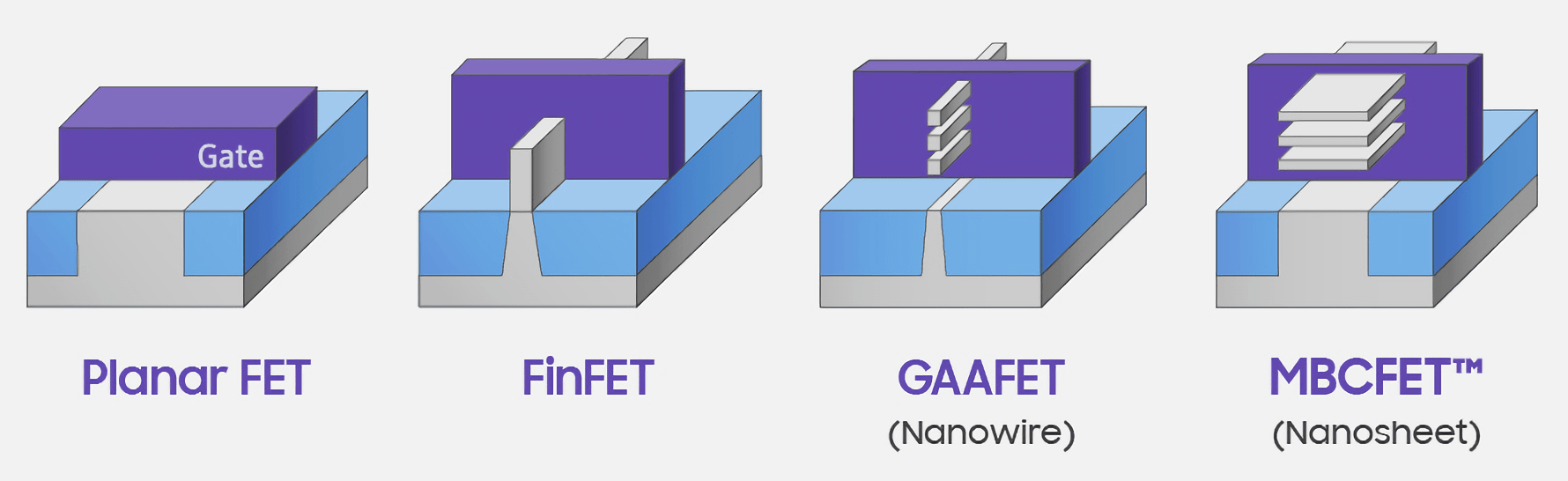

As AnandTech recounts, TSMC’s 3nm N3 node will continue to utilize FinFET transistors rather than switching to something like a Gate-All-Around (GAA) design a la Samsung. Compared to N5, N3 is expected to improve performance by 10-15 percent and boost power efficiency by as much as 25-30 percent.

Also in the cards is a 1.7x improvement in logic density.

Per TSMC’s roadmap, N3 will enter risk production in 2021 ahead of going into volume production sometime during the second half of 2022.

In the interim, consumers have a couple of other nodes to look forward to.

The aforementioned N5 node is expected to be used in Apple’s iPhone 12 family due out perhaps as early as next month. An optimization of this node, N5P, is also in the works that’ll boost performance and power efficiency by five and 10 percent, respectively, over the standard N5 node. N4 was also briefly mentioned, with risk production set to start in Q421 ahead of volume production the following year.

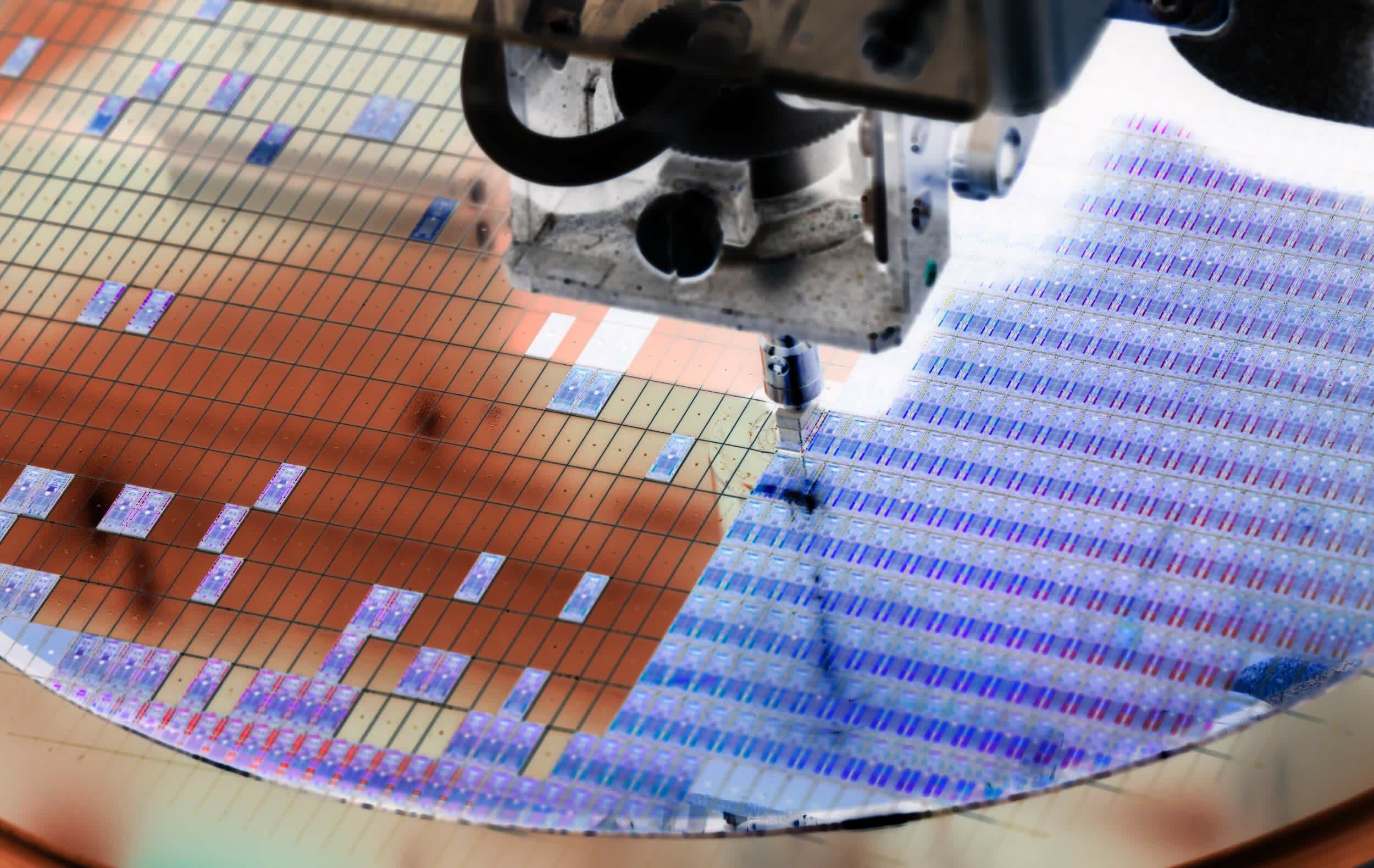

Image credit: Marco photo

https://www.techspot.com/news/86508-tsmc-3nm-n3-process-node-enter-volume-production.html