Why it matters: In the next few years, the microchip industry will witness significant technological advancements in the manufacturing processes for silicon components. TSMC is looking forward with full confidence, asserting that the company will provide nodes superior to those developed by its competitors.

Intel's futuristic 20A and 18A process nodes are expected to debut in new CPUs in 2024 or 2025. However, TSMC has already declared victory over the US company, with plans to introduce comparable manufacturing technology within the same timeframe, but with improvements across the board.

During a recent earnings call, TSMC CEO C.C. Wei stated that their internal assessment confirmed the enhancements of the N3P technology. TSMC's 3nm-class manufacturing node demonstrated "comparable PPA" (power performance area) to Intel's 18A node. N3P is expected to be even better, arriving earlier on the market, boasting "better technology maturity," and offering significant cost advantages.

Wei emphasized that TSMC doesn't underestimate or take the competition lightly. He also mentioned that the company's 2-nanometer technology, while still a work in progress, is expected to surpass both N3P and 18A. TSMC's 2nm-class manufacturing process is on track to become the most advanced technology in the semiconductor industry when it's introduced in 2025.

Intel is expected to release the first actual CPUs manufactured with the 20A process in 2024, bringing significant innovations to chip manufacturing technology with the introduction of RibbonFET gate-all-around transistors. RibbonFET represents the first major transistor redesign since the introduction of FinFET transistors in 2011 and will incorporate a new backside power delivery network (BSPDN) technology known as PowerVia.

At the same time, Wei confirmed that TSMC will continue to use the tried-and-true FinFET transistor technology, along with traditional power delivery methods, across its entire line of 3nm processes (N3, N3E, N3P, N3X). Gate-all-around transistors and BSPDN will be introduced with the N2 nodes, which are slated for high-volume production in the second half of 2025.

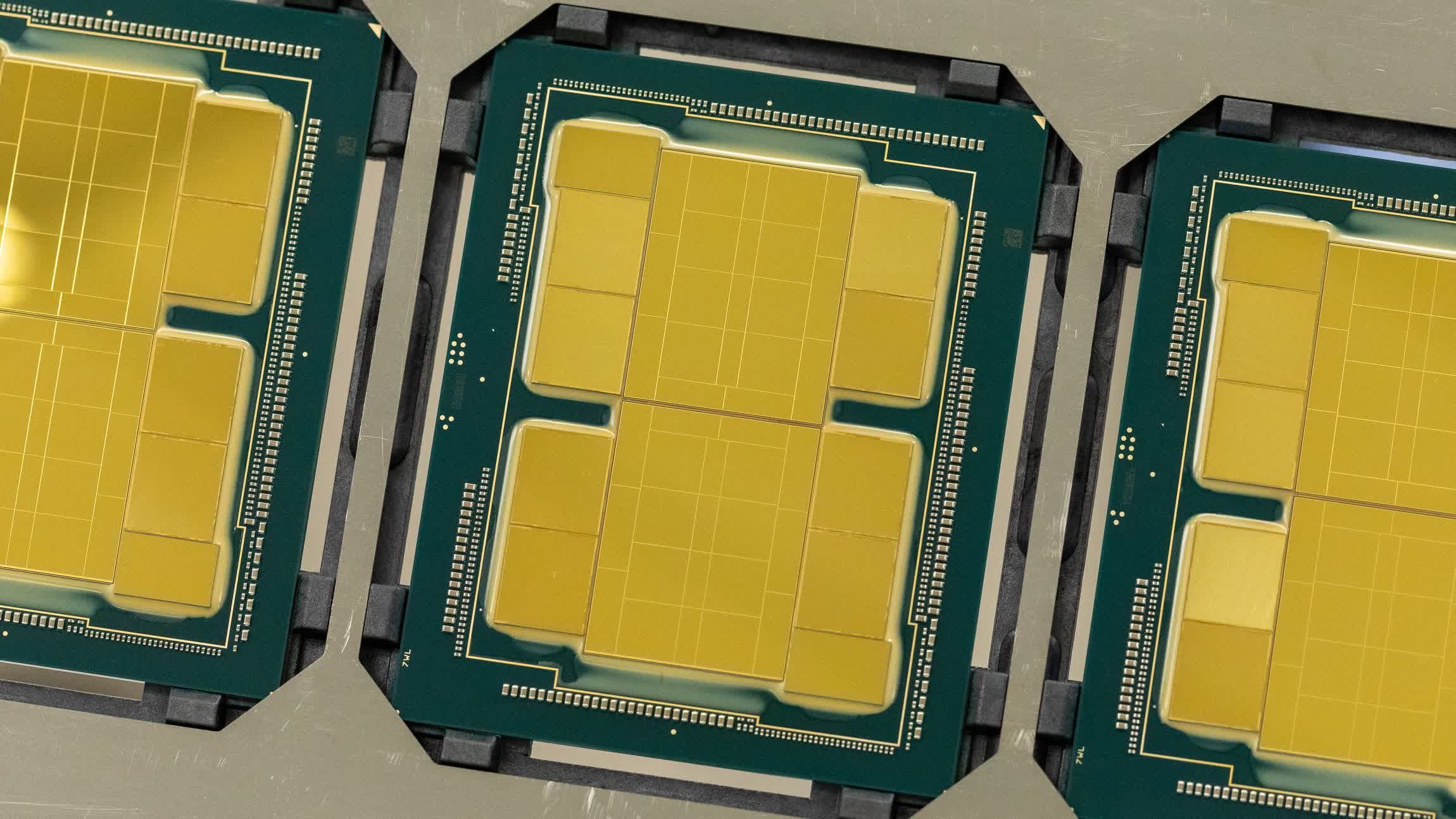

Wei mentioned that N3 is expected to contribute to a "mid-single-digit percentage" of TSMC's total wafer revenue in 2023, with a significantly higher percentage anticipated for 2024. There is strong demand for 3nm products from various customers who are seeking improved performance, power efficiency, yield, and "comprehensive platform support" for both high-performance computing (HPC) and smartphone applications.