Something to look forward to: With the arrival of Zen -- specifically, AMD's most recent Zen 2-based Epyc CPUs -- the complexion of the server landscape looks very different these days. Between now and 2021, with the upcoming Epyc Milan and Epyc Genoa, AMD will look to swing the server segment further in its favor with better IPC, reduced latency, and increased performance per watt.

At the HPC-AI Advisory Council UK conference, AMD divulged some details regarding its upcoming Zen 3 and Zen 4 architectures, as well as establishing a timeline for the next-gen Epyc Milan and Genoa processors.

AMD's Zen architecture and Epyc processors have been nothing short of a watershed moment for AMD in the server space, where a mere two short years ago, Intel held ~99% of the market. As things stand now, AMD could be on track to claw away as much as 10% of the lucrative market throughout 2020 and AMD looks to maintain its forward momentum hot off the heels of its Zen 2 Epyc "Rome" CPUs.

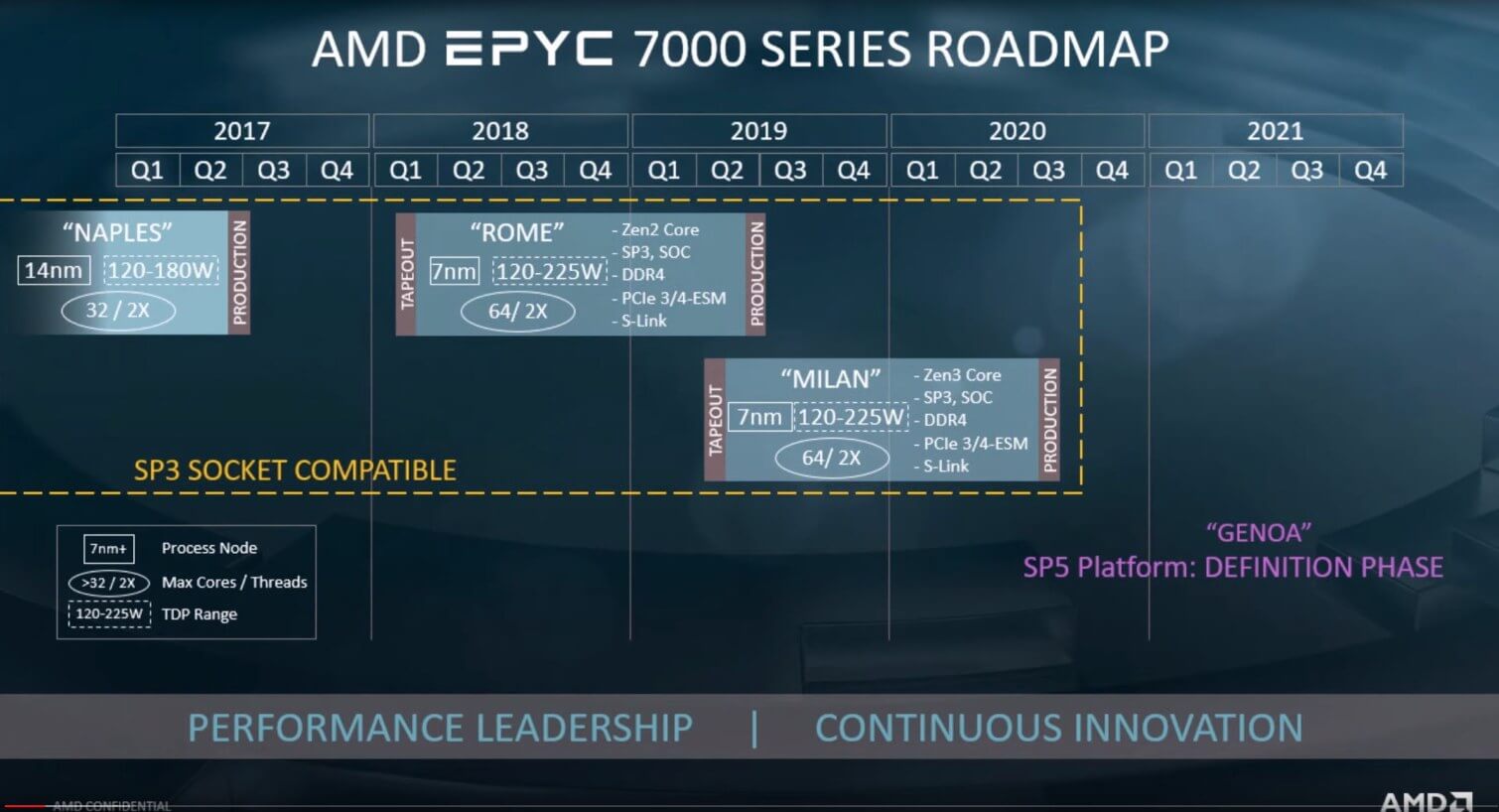

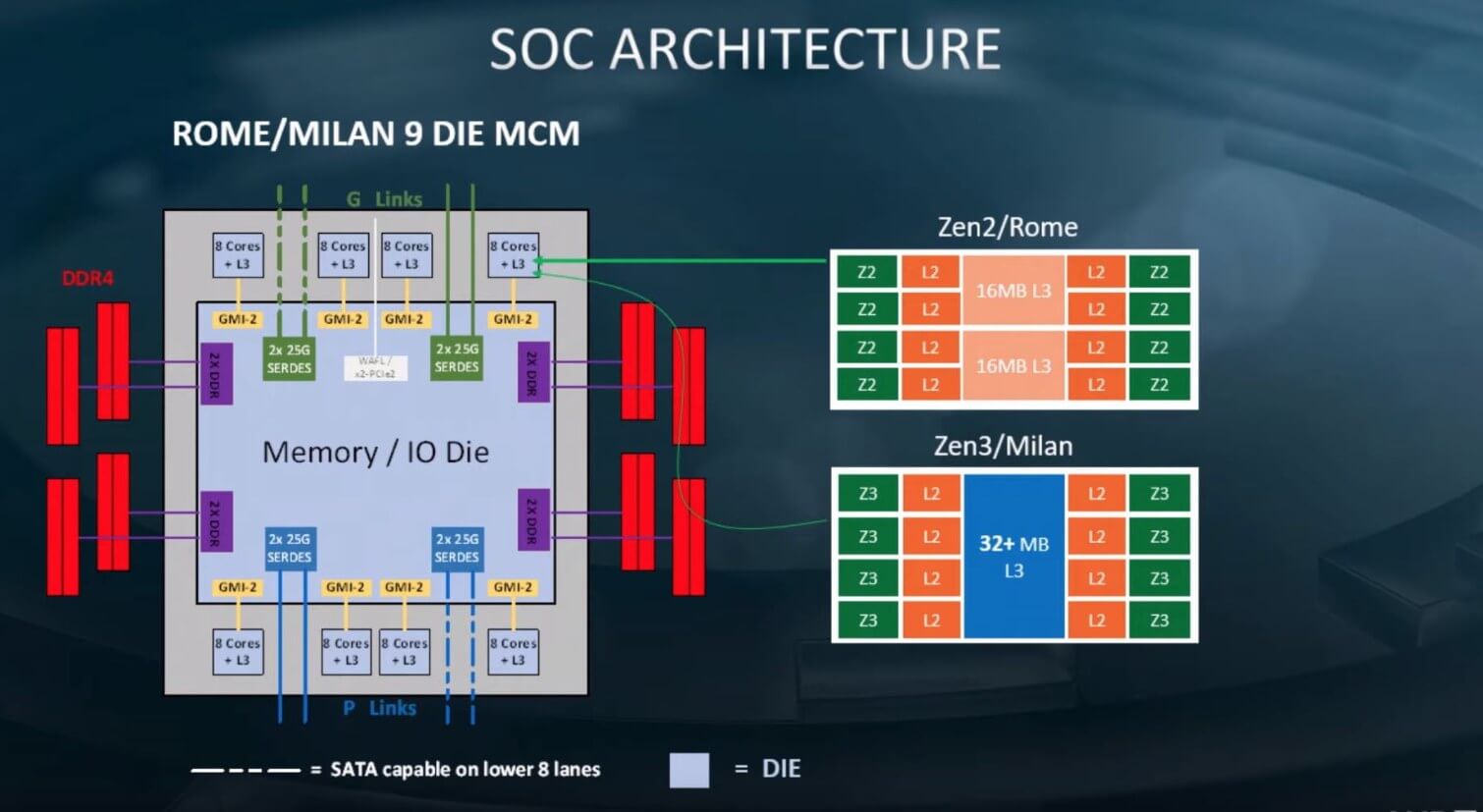

AMD set out to update its Zen architecture on a yearly basis, and this latest roadmap reiterates that. Milan is already in tape out, which means the chips are likely being sampled among some of AMD's closest customers. Milan will boast Zen 3 cores on a refreshed 7nm+ node, and should enter volume production in Q3 2020. Milan chips will scale up to 64 cores, the same as current-gen Rome, and drop into the same SP3 socket. Additionally, Milan looks to leverage 2 threads per core, putting to rest the rumor that it could come with as many as 4 threads per core.

Milan will also use the same nine-die configuration as Rome, with eight compute dies and one I/O die. However, it appears AMD will make some alterations under the hood, equipping each CCD (core complex die) with up 32MB of unified L3 cache.

Sitting out further on the horizon is Genoa, which will presumably use Zen 4 cores. Looking at the roadmap, Genoa will also signal the end for the SP3 socket, introducing the SP5 platform. Genoa would also arrive with support for DDR5 memory, and AMD is no doubt mulling a shift to PCIe 5.0. Genoa chips are currently in the "design" phase, and should land sometime in 2021.

https://www.techspot.com/news/82215-amd-details-zen-3-zen-4-alongside-roadmap.html