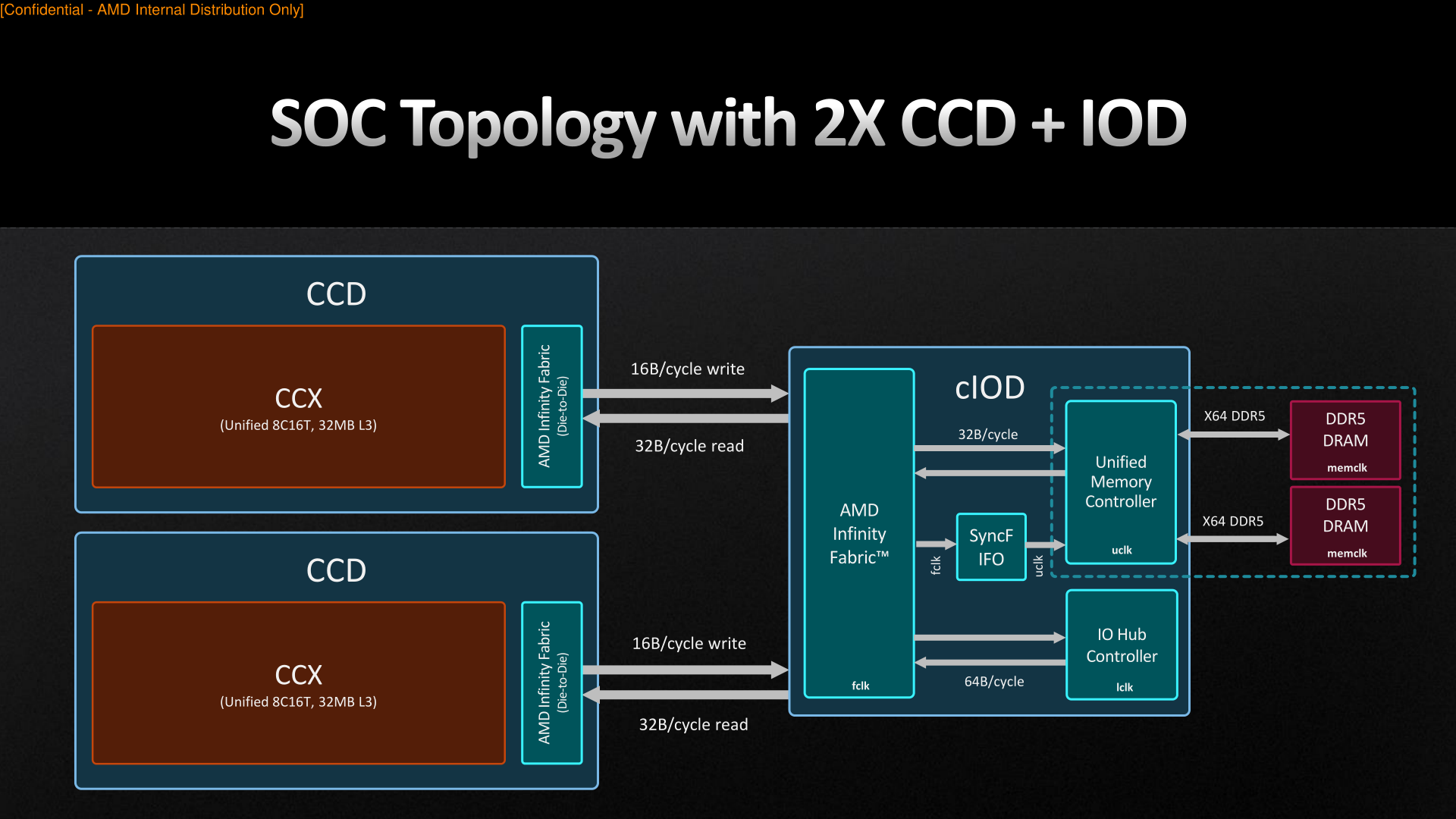

Why it matters: AMD's relationship with its AGESA microcode and the DDR5 memory standard has been rocky since the platform's launch in September of last year. From SOC voltage issues to instability above specific frequencies, problems with the platform have prevented users from pushing the limits of DDR5's capabilities.

Earlier this week, several AM5 motherboard manufacturers began rolling out AMD's latest AGESA update (1007B). According to reports from AM5 users and overclockers that received the update, the new firmware substantially increases AM5's overall DDR5 compatibility and support.

Before the update, 6000 to 6200 MT/s was considered the upper limit of AMD's DDR5 stability range. A tweet from Buildzoid outlined how the new update allowed the well-known tech guru and overclocker to reach speeds of 8,000 MT/s on a mid-tier AM5 motherboard.

Ryzen 7000. Running DDR5-8000. On a sub 300USD 8 layer daisy chain motherboard. This new BIOS is completely insanen. I might get DDR5-8000 stable on Ryzen before I ever get it stable on intel LOL. pic.twitter.com/96K334sUni

– Buildzoid (@Buildzoid1) July 19, 2023

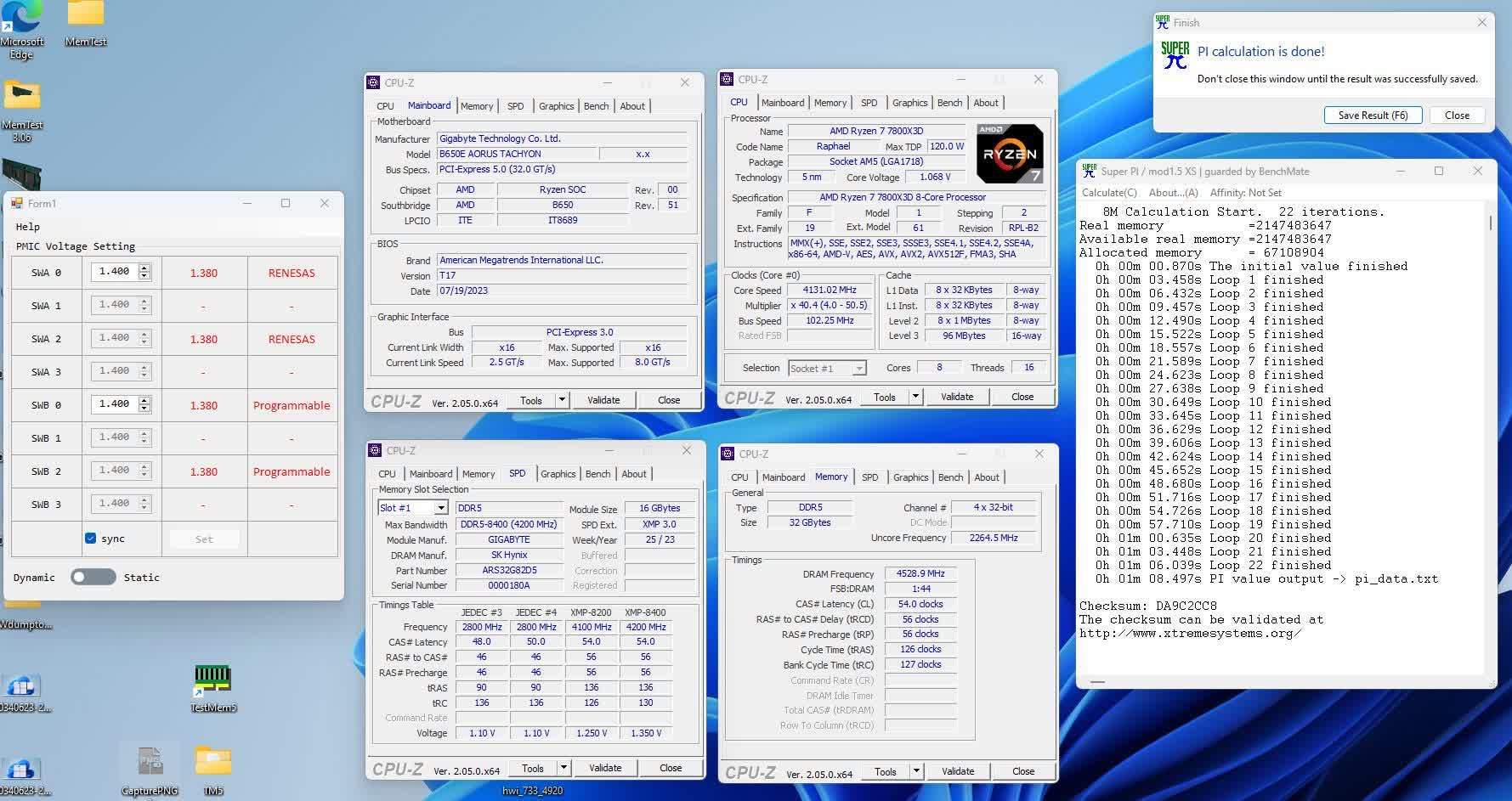

Another notable PC overclocker, Chihhua "HiCookie" Ke, managed to push his DDR5 even further thanks to the update, reaching a speed of 9,058MT/s on a set of Gigabyte's new Aorus DDR5-8400 memory. The minimal voltage required to sustain both the rated speed and the overclock is even more impressive.

Frequently higher speeds, tighter timings, and pushing beyond the limits of a memory module's rating can require substantial voltage increases. HiCookie managed to maintain the 9,000+ MT/s speeds on only 1.4v.

"This is absolutely bonkers," the overclocker said in a Facebook post proving the feat. "DDR5-9000 Just 1.4V on B650E Tachyon!"

HiCookie's overclock was achieved using a new Aorus Tachyon B650 motherboard, designed explicitly for overclocking enthusiasts. The board features two DIMM slots, advanced power delivery, enhanced memory layout and signaling support, and other overclocking-specific features designed to push the limits of the AM5 platform. HiCookie paired the board and RAM with a Ryzen 7 7800X3D processor for his overclocking attempts.

The 9,000 MT/s mark is a substantial milestone for the AM5 platform, as is the increase in supported RAM frequency and fabric clock stability. The overclocking successes from Buildzoid, HiCookie, and others occurred within a few days of the new code's release. With positive results like the new AGESA code and DDR5 support stacking up in AM5's win category, AMD may be on the cusp of turning yet another corner and quickly closing in on more of Intel's enthusiast-grade market share.

https://www.techspot.com/news/99505-ram-overclocker-breaks-9000-mts-barrier-am5-new.html